圖一:未來人工智慧模型普遍佈署高性能且低耗能之 AI 晶片。(影像來源: unsplash)

近年來因為爆量資料、高速電腦與演算法發揮相乘效果,人工智慧技術大幅進步,在眾多領域展現驚人的應用成效,例如 Google DeepMind 下圍棋的 AlphaGo 擊敗世界棋王震驚全球,為人類文明開啟了第四波革命。全球各先進國家莫不大力投入 AI 研發,全面佈署於行政、安全、醫療、交通、教育、科學、農業、工業與商業等領域。

科技部與清大攜手開發世界級類神經網路

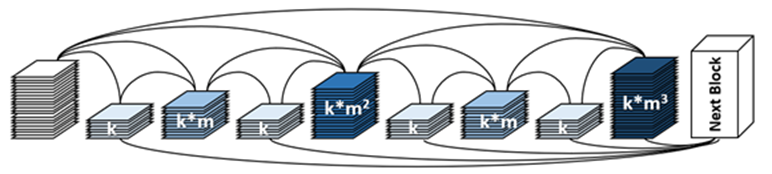

國立清華大學林永隆教授團隊在科技部半導體射月計畫 ( 2015 年 5 月至 2022 年 4 月)支持下開發出世界級的類神經網路 HarDNet Harmonic Densely Connected Neural Network (圖一) 具備精簡、準確、快速與省電之優點,在影像識別、物件偵測、影像分割等任務都獲得優異效果,在Papers-With-Code(旨在提供免費、開源的機器學習論文資料庫)上兩度獲得 State-Of-The-Art ( FC-HarDNet 在 Semantic Segmentation 語義分割項目,以及 HarDNet-MSEG 在 Polyp Segmentation 大腸鏡息肉分割項目) 。

甚至讓全球廿餘國研究機構與企業運用於自駕車、無人飛機、船舶安全、無人火車、無人倉儲、交通管理、醫療影像、衛星影像環境監測、半導體製造、資訊安全與工地安全等眾多領域。

圖二: 新型 CNN 類神經網路 HarDNet 架構圖(影像來源:林永隆教授)

半導體關鍵技術:高性能、低耗能之晶片設計

人工智慧計算需求分兩大類:訓練與推論,訓練階段仰賴通用圖形處理器 (GPGPU) 為主之超級電腦,推論階段則有多種方式。先進人工智慧模型之普遍佈署有賴高性能且低耗能之 AI 晶片,辨識一張影片所需的計算量已經超過播放一部電影所需的算量,所幸半導體製程技術隨著摩爾定律進步,繼續提供足夠、省電與低價之算力。

如何善用半導體之關鍵在於晶片設計,要設計最佳晶片有賴全盤優化之演算法、軟體、神經網路架構、計算機結構、電路與半導體製程。

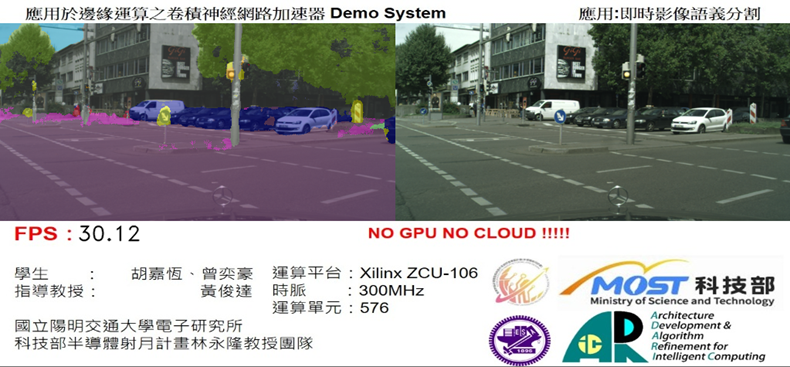

射月計畫之黃俊達教授團隊成功開發一個適用於邊緣運算之卷積神經網路(Convolutional Neural Network CNN)加速器。採用雙卷積器計算核心架構,可同時支援卷積與反卷積運算,具備執行物件偵測以及圖像語義分割(FC-HarDNet)高階影像處理任務之能力。於台積電 40 奈米製程下, 576-MAC 版本之操作頻率可達 1.25 GHz,效能峰值為 1.44 TOPS (每秒千億次運算),而能源效率值更高達 8.55 TOPS/Watt。

加速器之硬體架構具高度擴展性,配置之計算資源可輕易地隨任務所需增加或減少以確保最佳之性價比。圖二展示本加速器於自駕車關鍵技術之一,即時影像語義分割(real-time image semantic segmentation)上的應用。本加速器亦已證實可運用在物件偵測任務例如便利商店自動結帳系統等應用。

再以清華大學衍生之新創公司「創鑫智慧Neuchips Corp.」為例,該公司專注雲端資料中心推薦系統(Deep Learning Recommendation Model) 用 AI 推論晶片設計,採用 TSMC 7 奈米製程實現上述優化技術,只耗 20 Watts 便達到每秒可作兩仟萬次推論,是全世界唯一達到一次推論只耗 1 微焦耳(1 micro Joule/Inference)的產品。此項技術可以擴散到其它應用領域,也會擴散到消費性產品。

圖二: HarDNet 神經網路硬體加速器於自駕車關鍵技術 – 即時影像語義分割上之應用(影像來源:林永隆教授)

AI 晶片需求超越以往、大幅提升各產業競爭力

晶片應用範圍從 PC(辦公室)、手機(個人) 到 IOT (物聯網) 愈來愈廣泛,AI 晶片的需求將十倍甚至百倍於過往之總合,我國電子、半導體產業與研究有相當好的基礎,迎向未來大潮流站在極佳的出發點。善用 AI 晶片與系統之功能就如上一代善用網際網路數位科技一樣,將大幅提升各行各業之生產力與國際競爭力,進而促進全體國人之福祉。

本著作係採用 創用 CC 姓名標示─非商業性─禁止改作 3.0 台灣 授權條款 授權.

本授權條款允許使用者重製、散布、傳輸著作,但不得為商業目的之使用,亦不得修改該著作。 使用時必須按照著作人指定的方式表彰其姓名。

閱讀授權標章或

授權條款法律文字。