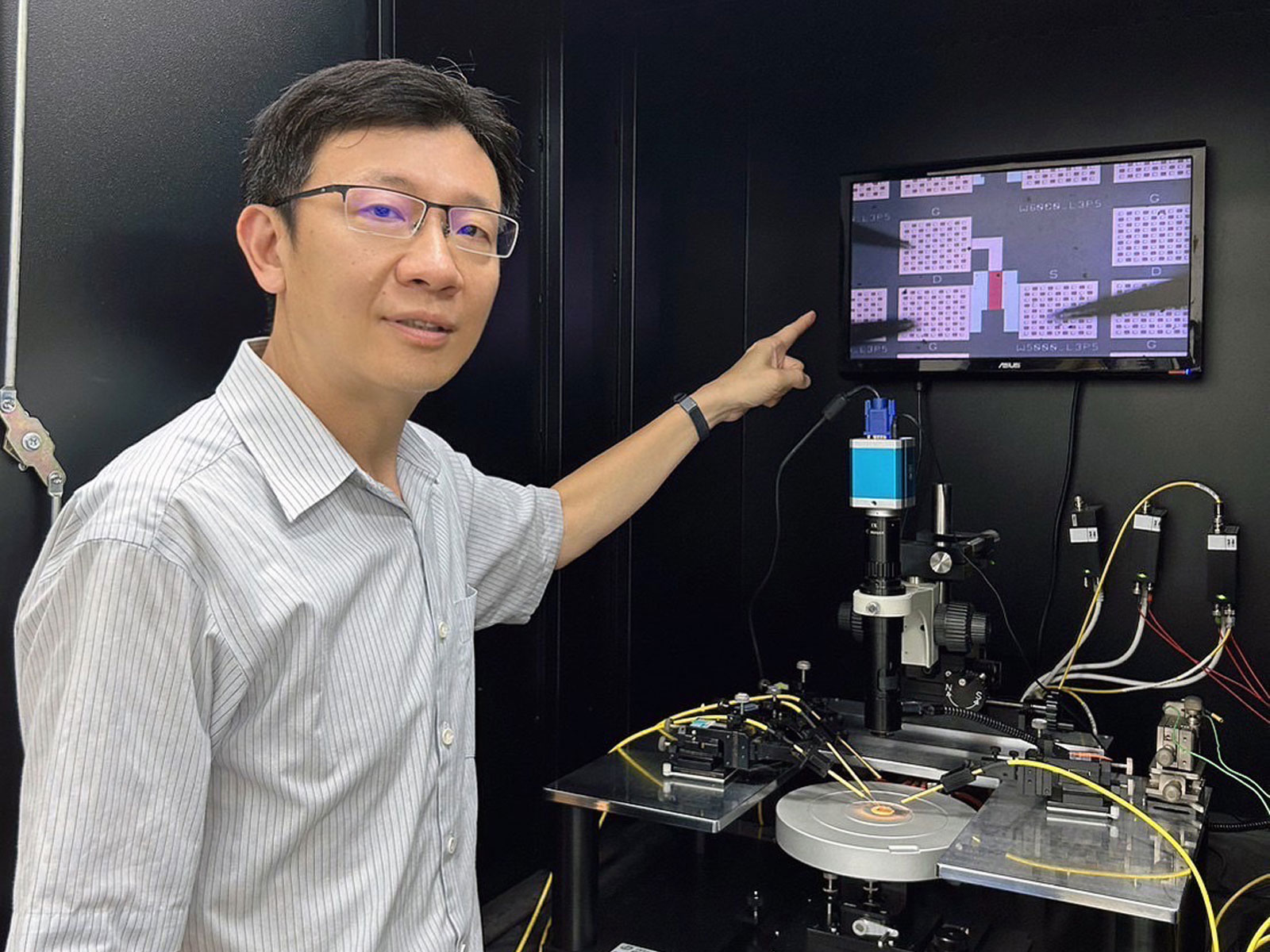

陽明交通大學光電工程系劉柏村教授團隊成功開發「單晶片三維異質半導體堆疊技術」(Monolithic 3D-stack Heterogeneous Semiconductor Introduction, M3D)。圖片來源:劉柏村教授提供

隨著人工智慧(artificial intelligence, AI)技術的快速發展,需要更多的計算力、記憶體容量,以及更大規模的異質整合技術發展,AI 晶片中的電晶體數量將隨之持續增加。例如,輝達(NVIDIA)最新的圖形處理器晶片 Blackwell,就是使用台積電的 N4P 製程,其晶片上約有 2,080 億顆電晶體,規模相當驚人。

為了在晶片中增加更多電晶體,以提升晶片的運算力,半導體產業不僅在先進製程上持續創新,還改進了晶片架構,將晶片從原本的單層電路設計轉向多層電路堆疊,使晶片走向立體(3 dimensions, 3D)電路架構。想像一下,未來的晶片裡會有數百億甚至數千億個電晶體,就像一座超大型摩天大樓,每一層都有數不清的房間在運算。

不過,目前市面上的 3D 晶片,大多數採用 2.5D 封裝技術,就是將多塊獨立的晶片透過先進封裝技術堆疊在一起。就像是蓋樂高積木時,一層一層往上堆疊,但每一個樂高積木都是一個獨立的晶片,最後透過封裝技術推壘成一個很大的樂高積木,但其本質仍然是多晶片系統,而非真正意義上的單晶片 3D 堆疊。

為了達到「真 3D」,陽明交通大學光電工程系劉柏村教授在國科會「Å 世代前瞻半導體專案計畫」支持下,成功開發「單晶片三維異質半導體堆疊技術」(Monolithic 3D-stack Heterogeneous Semiconductor Introduction, M3D)。

單晶片堆疊:解鎖3D晶片的無限潛能

劉柏村教授解釋,藉由封裝技術將多片晶圓片堆疊成 3D 晶片的技術,稱為矽穿孔(Through Silicon Via, TSV)技術。TSV 的孔徑(孔直徑約 5 ~ 10 µm,孔深度約20 ~ 50 µm)是為了讓不同層晶圓之間的電路訊號可以互相流通,就像蓋房子時,需要有樓梯或電梯讓不同樓層的人員通行,但樓梯太大會佔據晶片內部的寶貴空間,讓其他電路元件無法緊密排列,降低了電路的密集度。再者,鑽孔的規格、可用材料、TSV 的位置、堆疊和接合的精密度,都需要統一標準,這也限制了製程的彈性。

這個過程還有其他挑戰。例如為了在一定空間內堆壘更多層晶圓,需要藉由研磨和蝕刻將晶圓薄化,但過程中可能產生破片或裂痕等損傷,任何一層晶圓出現瑕疵,就會導致電路功能受損,降低良率。

單晶片三維異質半導體堆疊技術,則是從頭到尾都使用同一片晶圓片作為基板,利用奈米級的半導體製程工藝,將多層電晶體和積體電路(integrated circuit, IC)一層一層地堆疊起來。各元件層的連接是藉由微小引洞結構(孔直徑約 50 nm,孔深度約 100 nm)連通,待所有電路製作完成後,再把整片晶圓切割成 3D 晶片,不需要將多片晶圓片對準,也不需要進行晶片減薄和鍵合的繁瑣工藝。就像直接用一大塊水泥蓋房子,直接在水泥上刻出許多層電晶體和 IC 電路,不需要擔心不同材料之間的接縫問題、不需要花費時間去確保每層樓是否對準、不需要把層樓打磨得更薄來適應彼此的尺寸。

此外,目前製作晶片都著重於體積及厚度越小越好、密度越高越好。但是,多晶片堆疊技術中,一片晶圓的厚度大約有 600,000 nm。相較之下,單晶片堆疊技術中,每一層電晶體組成的 IC 電路層厚度僅為 100 nm,不同層之間的連接厚度約 500 至 1,000 nm,加總起來遠低於多片晶圓片堆疊的厚度。由於單晶片堆疊在有限面積下大幅提高電晶體元件數量與電路的密集度,是一種體積更小、成本效益更高的 3D 晶片製造技術,有望超越摩爾定律(More than Moore’s),為進一步的製程微縮帶來希望。

然而,單晶片堆疊技術的挑戰在於,元件堆疊左右於熱穩定性、平坦度、元件電性匹配等因素,其中不同階段製程的溫度與時間也需要嚴格控制,讓製成的電晶體元件及電子電路仍能維持優異的電性效能與可靠度。

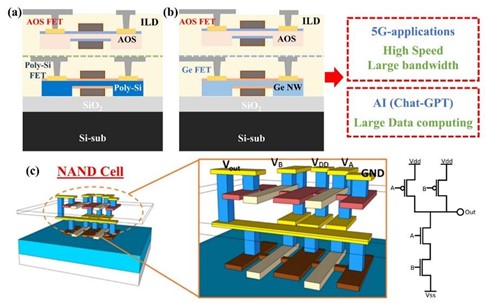

劉柏村教授團隊開發的「單晶片三維異質半導體堆疊技術」之高密度反及閘(NAND)電路架構示意圖。圖片來源:劉柏村教授提供

新穎半導體材料,打造下一代埃米級單晶片

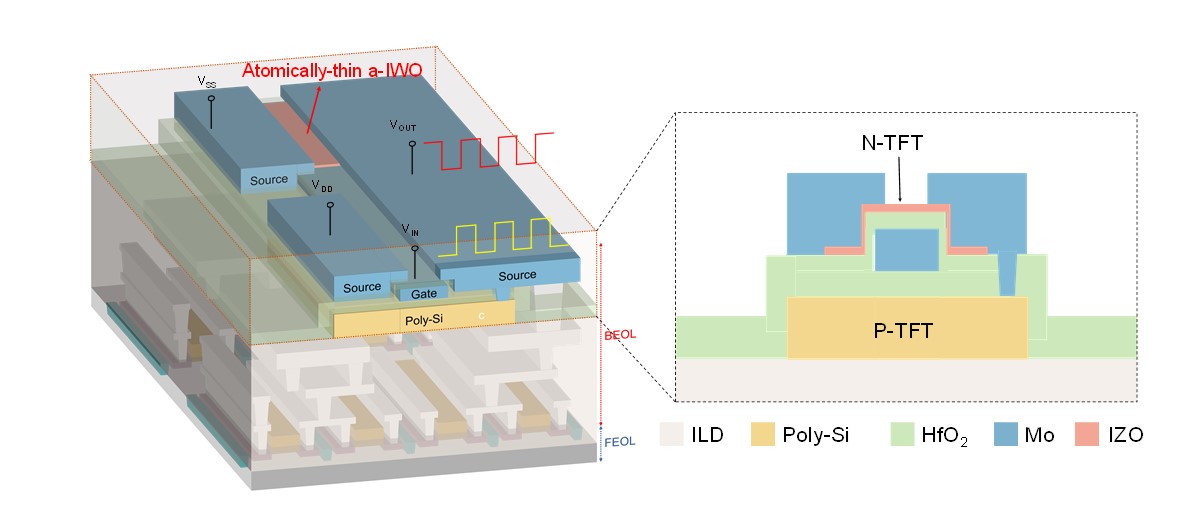

劉柏村教授研究團隊的創新突破在於,採用新穎的氧化物半導體材料——氧化銦鎢(amorphous indium tungsten oxide, a-IWO),搭配複晶矽薄膜電晶體,整合成單晶片三維積體電路下的垂直式「互補式場效電晶體」(Complementary Field-effect transistor, CFET),並成功以反相器邏輯電路(inverter,又稱 NOT gate)進行驗證。這項技術不僅讓晶片中的電路密集度大幅增加,還具有高電壓增益、低功耗和高雜訊邊限等優點。

這是怎麼做到的呢?首先,在底層製作完成複晶矽薄膜電晶體元件,然後在其上方堆疊氧化銦鎢薄膜電晶體。值得注意的是,氧化銦鎢通道層的厚度僅有 2.5 nm,呈現出近似二維材料的特性。這種設計可以有效抑制電晶體漏電路徑與短通道效應(Short Channel Effects, SCE),使其展現出色的元件性能。

這項技術的成功研發,使得立體堆疊邏輯閘電路擁有高電壓增益、低功耗和高雜訊邊限等特性,能在有限的晶片面積中實現超高的電路密度,並整合更多功能電路,展示出製作下一代埃米級單晶片三維積體電路技術的巨大潛力。這不僅為超高運算力的 AI 晶片製造提供了可能性,相關研究成果也於 2023 年發表在國際知名學術期刊《尖端科學》(Advanced Science)。

可應用於單晶片三維積體電路之垂直堆疊互補式異質結構場效電晶體。圖片來源:劉柏村教授提供

走在前沿:臺灣如何在 AI 晶片競賽中領跑

當 AI 正在全球範圍內掀起革命之時,這項研究進一步鞏固了臺灣在全球半導體產業中的領導地位。

「單晶片三維異質半導體元件整合技術有著巨大的應用潛力」,劉柏村教授強調。為了進一步優化單晶片三維異質半導體堆疊技術,劉柏村教授提出了多項策略。首先,團隊將持續改進氧化銦鎢的特性,包括通道厚度和組成比例等。其次,他們將深入研究三維堆疊式結構,優化上層與下層元件之間的界面和相互作用,並加強每層元件表面的平坦度。此外,還會發展更先進的製造技術,實現更高的製程控制和一致性,將單晶片三維異質半導體堆疊技術進行系統級整合。

臺灣不僅擁有眾多技術人才和先進的製造設備,還以其創新能力和卓越的製造工藝,在半導體行業中占據重要地位。劉柏村教授的研究成果展示了臺灣的半導體技術創新能力,並為臺灣的半導體企業提供了加速開發下一代 AI 晶片的機會,進一步鞏固我們在全球市場中的領導地位。這些創新技術不僅可以提高臺灣在全球半導體市場的競爭力,還能擴大市場份額。

陽明交通大學光電工程系劉柏村教授(前排中)研究團隊。圖片來源:劉柏村教授提供

本著作係採用 創用 CC 姓名標示─非商業性─禁止改作 3.0 台灣 授權條款 授權.

本授權條款允許使用者重製、散布、傳輸著作,但不得為商業目的之使用,亦不得修改該著作。 使用時必須按照著作人指定的方式表彰其姓名。

閱讀授權標章或

授權條款法律文字。