<

貝爾實驗室(Bell Labs)於 1947年開發出世界第一個電晶體,並於1948年7月15日將之發表於《物理評論快報》(Physical Review Journals),圖片為Lucent Technologies公司於1997年所製作的複製品。(圖片作者:Wikipedia user Federal employee,公有領域)

電子科技發展迄今數十多年,已讓整個高科技產業的產品都脫離不開電子元件的使用,而在諸多的電子元件中,『電晶體』扮演著最關鍵核心的角色。一般常聽到的電子元件大概就是『電阻』、『電容』、『電感』等被動元件,它們之所以稱為被動元件是因為該元件不會對電子訊號產生增益的效果,也就是無法放大電子訊號。故能對電子訊號提供增益效果的元件就稱為主動元件。而在以電子電路或是積體電路所構建而成的晶片中,主要就是靠半導體所製成的『電晶體』來對電子訊號進行調變或是開關的作用,以達到預期的功能,因此電晶體可說是各種高科技產品中的靈魂元件!

『電晶體』大致可分為兩類,分別為『雙極性接面電晶體(bipolar junction transistor, BJT)』與『場效電晶體(field-effect transistor, FET)』。而對於積體電路的設計,若想要追求電子晶片功能的提升,除了仰賴電路設計者的功力之外,電晶體元件的性能也是相當重要。舉例而言,電子元件就是像是小積木一樣,利用一堆小積木可以拼湊出各式各樣的事物,像飛機、汽車、城堡等;而電路設計者就像是拼積木的人,電路圖就像是拼裝說明書,若要製作出功能良好的事物,除了需要依賴積木拼裝設計的能力之外,積木本身的功能性也是很重要的一環。

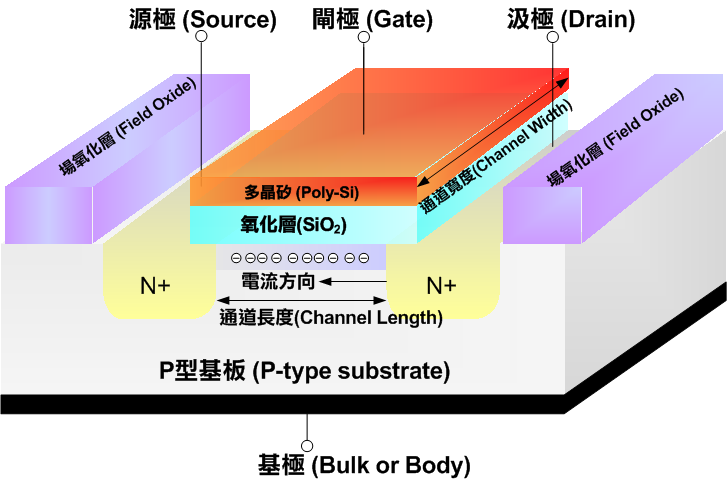

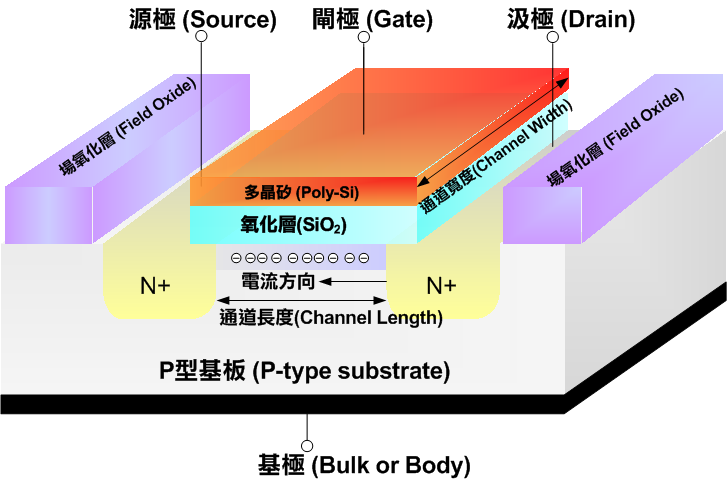

目前各類型的電晶體當中,以『金屬氧化物半導體場效電晶體(Metal-Oxide-Semiconductor Field-Effect Transistor, MOSFET)』為電路設計的主流元件。它的結構並不複雜,具有四端電極,分別為閘極(Gate)、汲極(Drain)、源極(Source)與基極(Bulk or body)。閘極到基極這兩端點之間是一個MOS電容結構,汲極與源極之間則為元件的電流通道(Channel),而此通道的產生就是依靠MOS電容來調變通道的電流大小,藉此控制電子訊號的開與關或是放大效果。因此,目前生產超大型積體電路(very-large-scale integration, VLSI)的主要晶圓代工廠如台積電、聯電、三星、英特爾等國際大廠,均以開發『MOSFET』為主要目標。

n型MOSFET結構示意圖。(圖片作者:Wikipedia user LeviLee,公有領域)

n型MOSFET結構示意圖。(圖片作者:Wikipedia user LeviLee,公有領域)

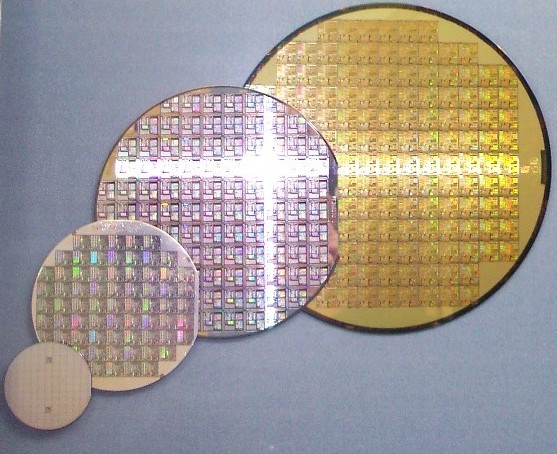

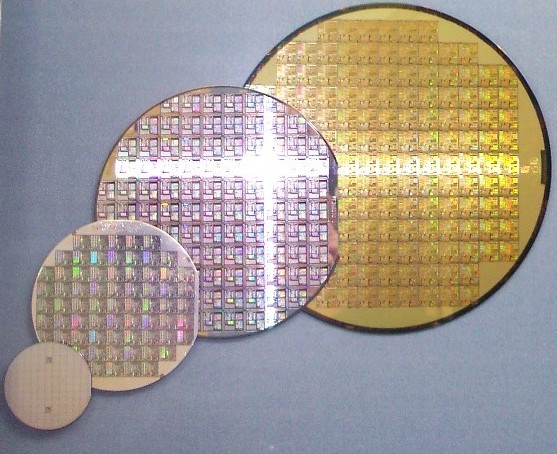

積體電路是一種在矽晶圓上製作電子電路的技藝,所以製作這類型產品的公司又稱為晶圓廠。仔細觀察晶圓,可看到上頭有一個個的小方塊,那東西就是一個單獨的晶片電路,稱為『晶粒(Die)』,把晶粒經後續的封裝過程處理過後,就成為了所謂的『晶片(Chip)』。而MOSFET的開發,主要是以元件微小化為最大重點,因為元件的微小化可以直接帶來兩個好處,首先是元件縮小後,由元件所構成的電路或晶粒面積也可以隨之縮小,那麼同樣面積的晶圓可以生產的晶粒數量就會增加,如此一來每一個晶片的製造成本就會降低了,因此在VLSI製程技術就逐漸朝向晶圓面積越做越大,但電子元件越做越小的趨勢發展。

至於第二個優點就是元件既然變小了,那在同樣的晶片面積上將可塞入更多的元件,功能應該就可以增加,或是可提供更大的設計空間來提升晶片內電路的效能!於是整個VLSI產業的發展就形成了:使用的晶圓面積越來越大(一般以晶圓直徑長度與英吋單位命名,比如4吋→6吋→8吋→12吋晶圓),而MOSFET製程技術讓元件關鍵尺寸越來越小(22/20奈米→16/14奈米→10奈米→7奈米→5奈米→3奈米…)。從上述的趨勢可以看到越先進的MOSFET製造技術其數字越小,這稱之為技術節點(technology node)。

矽晶圓的尺寸差異與晶片圖案。(圖片作者:Wikipedia user Stahlkocher,CC BY-SA 3.0授權)

矽晶圓的尺寸差異與晶片圖案。(圖片作者:Wikipedia user Stahlkocher,CC BY-SA 3.0授權)

而這些在報章雜誌上常出現的技術節點名詞也非常的有趣,在早期,電晶體的最小關鍵尺寸在微米(百萬分之一公尺)時,當進入到小於1微米的技術節點,就稱此階段為『次微米(sub-micron)』時代,而進入到比0.1微米(千萬分之一公尺)更小的技節點就稱之為『深次微米(deep sub-micron)』時代,但0.1微米其實就是100奈米,因此後來又將『深次微米』這一詞改稱為『奈米』。電晶體的每一個技術世代所想要達成的微縮目標是想讓相同電路所構成的晶片面積縮小為原來的一半,那麼對於晶片的長度與寬度就各要縮小成原來的0.7倍,也造成了每一個VLSI的技術節點數字是以0.7倍的倍數因子在縮小與命名。

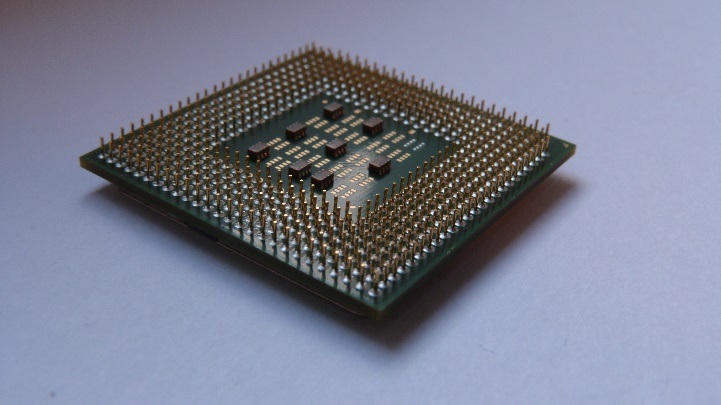

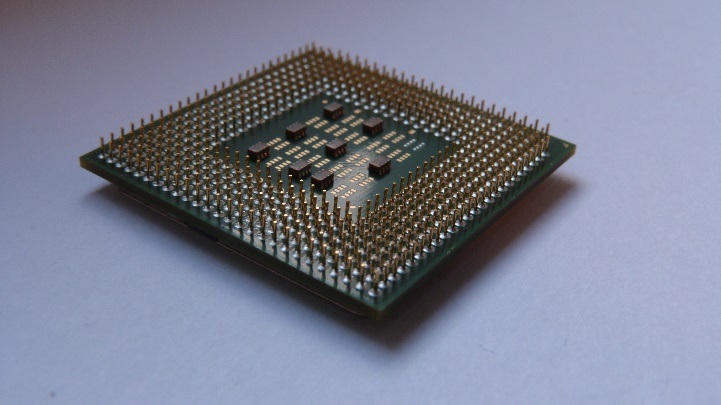

晶粒封裝後所形成的晶片。(圖片作者:Wikipedia user Liam McSherry,CC BY-SA 3.0授權)

晶粒封裝後所形成的晶片。(圖片作者:Wikipedia user Liam McSherry,CC BY-SA 3.0授權)

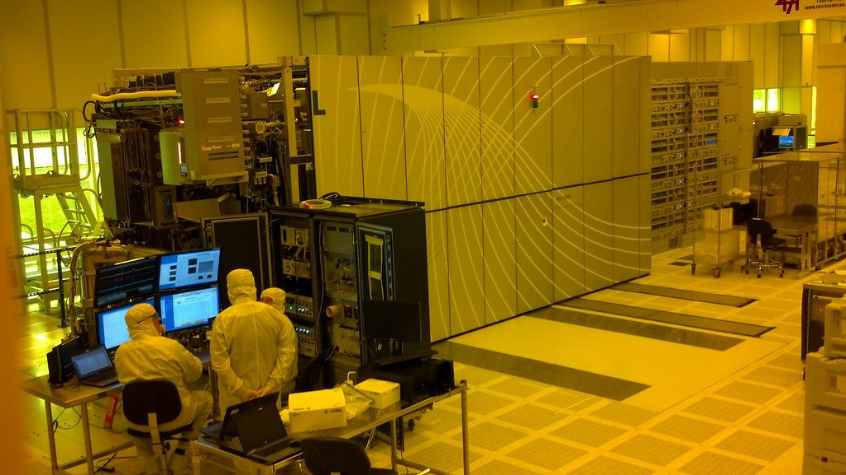

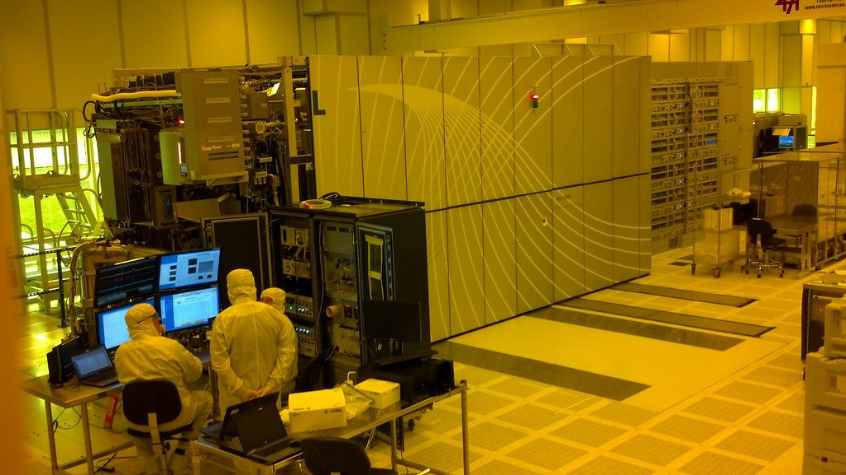

而在早期的次微米時代,元件的微小化常會伴隨產生電特性的副作用,此稱為短通道效應(short-channel effect)。為了改善短通道效應,需要對MOSFET的內部進行局部摻雜製程,並且引用新型的熱處理方式,換句話說,為了改善元件微小化時所導致的不完美電特性,就必須引進新的製程技術,所以對應的製程機台設備商也會扮演著技術的推手,他們必須提供可以滿足晶圓廠所需要的製程設備。此一話題最具代表性的莫過於:當VLSI進入7奈米製程後,微小化尺寸所需要的微影製程技術,即極紫外光源系統(簡稱EUV),單一機台的價格就高達上億美金,可知VLSI產業的投入門檻會有多高的資金需求。

製作奈米尺寸的電晶體時用的EUV光刻(lithography)系統。(圖片來源:IBM Research,CC BY-ND 2.0授權)

製作奈米尺寸的電晶體時用的EUV光刻(lithography)系統。(圖片來源:IBM Research,CC BY-ND 2.0授權)

除了電晶體微小化時所需搭配的新設備引進外,在奈米技術節點時,對電晶體的需求已經不只是尺寸微縮而已,甚至還更要求元件特性的加強!因為高科技產品的發展太過迅速,從十幾年前的主流產品『電腦』,發展到今日的『智慧型手機』,大眾對於晶片的運算速度需求越來越高,而這也加速了電晶體在增強性能方面的需求。因此在奈米世代的電晶體製程中,又得引進應力技術(strain)來改變材料的特性,進而提升元件的電流密度。而除了應力技術之外,新的材料也被引用來取代傳統的矽(Si)半導體與二氧化矽(SiO2)絕緣層,如矽鍺化合物(SiGe)、高介電常數絕緣層/金屬閘極(簡稱high-k/metal-gate,HK/MG)就是甚具潛力的新材料。

具SiGe汲極/源極與HK/MG材料之MOSFET結構示意圖。(圖片作者:Wikipedia user Cepheiden,CC BY-SA 3.0授權)

具SiGe汲極/源極與HK/MG材料之MOSFET結構示意圖。(圖片作者:Wikipedia user Cepheiden,CC BY-SA 3.0授權)

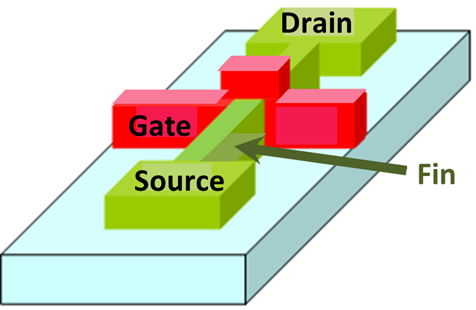

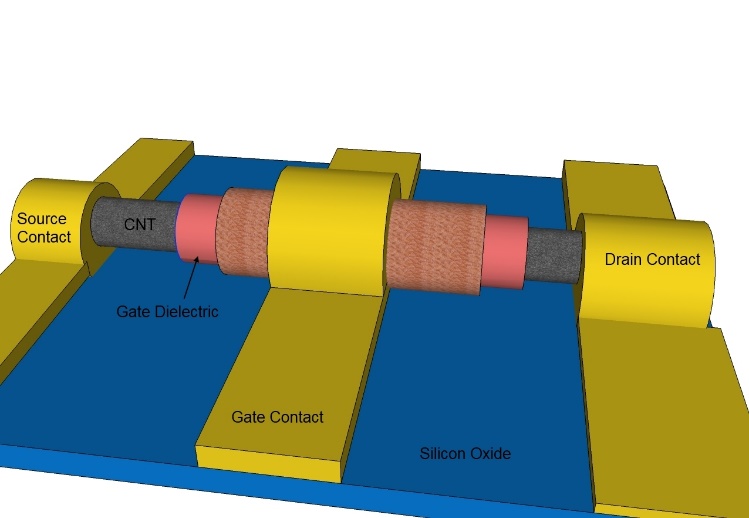

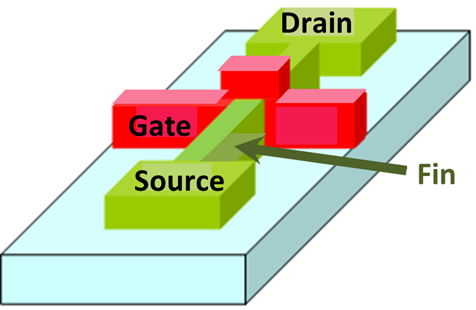

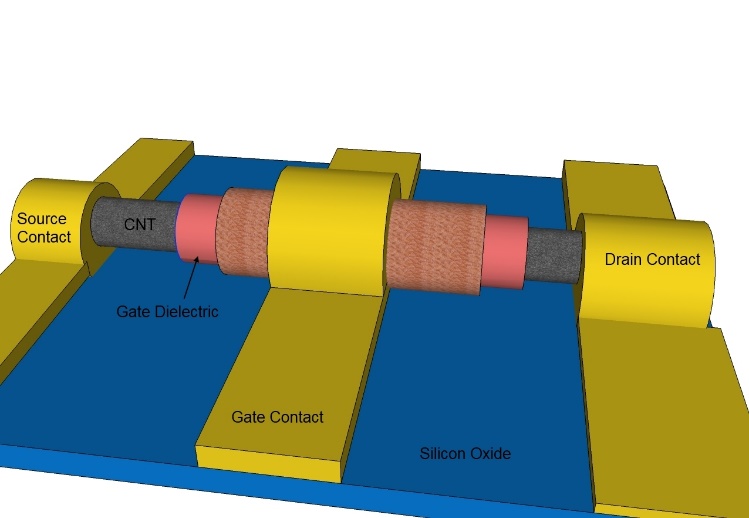

科技的需求與發展是無止境的,在引進新材料後,奈米技術進入至16/14節點時,原本的電晶體結構已無法滿足電性的需求,因此原本平面結構的電晶體被改為立體結構的通道形狀,由於其形狀如同魚鰭一般,故又稱為鰭式電晶體(Fin-FET)。Fin-FET可大幅改善電晶體尺寸縮小時因短通道效應所造成的漏電流,減少了電晶體在關閉狀態下的功率損耗。由於手持式智慧產品的流行,電子產品不須一直插著電源線,而是依賴電池提供電力運作,因此對於電路晶片的低功率損耗要求極嚴,這也導致現在VLSI一直朝向低功率元件的目標持續開發新一代的電晶體。綜觀目前電晶體技術的發展,對於未來的5奈米、3奈米乃至於2奈米技術節點以後的電晶體,在結構上很可能會再做改變,下一世代的結構目前一般猜測以閘極全包覆(Gate-all-around,GAA)結構的呼聲較高。

FinFET結構示意圖。(圖片作者:Wikipedia user Irene Ringworm,CC BY-SA 3.0授權)

FinFET結構示意圖。(圖片作者:Wikipedia user Irene Ringworm,CC BY-SA 3.0授權) GAA-FET結構示意圖。(圖片作者:Wikipedia user Popproject3,CC BY-SA 3.0授權)

GAA-FET結構示意圖。(圖片作者:Wikipedia user Popproject3,CC BY-SA 3.0授權)

電晶體的發展除了上述的VLSI技術演進之外,下一個殺手級的應用又是什麼呢?目前全世界最熱門的高科技發展方向應以人工智慧(AI)奪冠,而人工智慧的發展須仰賴機器的自我深度學習技術以及利用龐大資料庫的『大數據』分析處理能力才能使機器達到智慧反應。而在人工智慧的發展過程中,因涉及到龐大資料的運算處理,因此對於硬體的高速運算需求也扮演著不可或缺的角色,由此可觀察到超級電腦的硬體需求。於是乎發展出具超高速運算能力的電腦將會是未來的發展方向之一,這也引發了近期在科技界討論度狂升的另一個主題:『量子電腦』。

除了量子電腦的遠景被看好之外,物聯網(IoT)也是另一項快速崛起的應用科技,IoT簡單的說,就是將各項電子產品通過網路連線來進行遠端遙控與資料收集,最終可作為AI所需要的『大數據』提供資料來源。以簡單的比喻來說,量子電腦可說是AI的大腦,而IoT就是接受訊號與執行指令的感官與手腳!而這些科技發展的可能性也將以半導體電子元件來實現,因此,對於電晶體的將來,應該還有很大的發展空間,就讓我們拭目以待這個世界的科技會走到什麼境界吧!

<

IoT概念示意圖。(圖片作者:pixabay user jeferrb,自由使用)

責任編輯:郭啟東/國立中山大學

<貝爾實驗室(Bell Labs)於 1947年開發出世界第一個電晶體,並於1948年7月15日將之發表於《物理評論快報》(Physical Review Journals),圖片為Lucent Technologies公司於1997年所製作的複製品。(圖片作者:Wikipedia user Federal employee,公有領域)

<貝爾實驗室(Bell Labs)於 1947年開發出世界第一個電晶體,並於1948年7月15日將之發表於《物理評論快報》(Physical Review Journals),圖片為Lucent Technologies公司於1997年所製作的複製品。(圖片作者:Wikipedia user Federal employee,公有領域) n型MOSFET結構示意圖。(圖片作者:Wikipedia user LeviLee,公有領域)

n型MOSFET結構示意圖。(圖片作者:Wikipedia user LeviLee,公有領域) 矽晶圓的尺寸差異與晶片圖案。(圖片作者:Wikipedia user Stahlkocher,CC BY-SA 3.0授權)

矽晶圓的尺寸差異與晶片圖案。(圖片作者:Wikipedia user Stahlkocher,CC BY-SA 3.0授權) 晶粒封裝後所形成的晶片。(圖片作者:Wikipedia user Liam McSherry,CC BY-SA 3.0授權)

晶粒封裝後所形成的晶片。(圖片作者:Wikipedia user Liam McSherry,CC BY-SA 3.0授權) 製作奈米尺寸的電晶體時用的EUV光刻(lithography)系統。(圖片來源:IBM Research,CC BY-ND 2.0授權)

製作奈米尺寸的電晶體時用的EUV光刻(lithography)系統。(圖片來源:IBM Research,CC BY-ND 2.0授權) 具SiGe汲極/源極與HK/MG材料之MOSFET結構示意圖。(圖片作者:Wikipedia user Cepheiden,CC BY-SA 3.0授權)

具SiGe汲極/源極與HK/MG材料之MOSFET結構示意圖。(圖片作者:Wikipedia user Cepheiden,CC BY-SA 3.0授權) FinFET結構示意圖。(圖片作者:Wikipedia user Irene Ringworm,CC BY-SA 3.0授權)

FinFET結構示意圖。(圖片作者:Wikipedia user Irene Ringworm,CC BY-SA 3.0授權) GAA-FET結構示意圖。(圖片作者:Wikipedia user Popproject3,CC BY-SA 3.0授權)

GAA-FET結構示意圖。(圖片作者:Wikipedia user Popproject3,CC BY-SA 3.0授權) <IoT概念示意圖。(圖片作者:pixabay user jeferrb,自由使用)

<IoT概念示意圖。(圖片作者:pixabay user jeferrb,自由使用)