IC的製程簡單來說,是在矽晶圓上製造出一個電路構造,其中包括許多半導體元件,以及彼此連接的金屬線等。這個製造過程極其複雜,因為我們必須在晶圓上放上各式各樣的材料,並將材料做成想要的電路圖案,需要使用的製程包括微影、蝕刻、沉積等等。而微影貫穿整個IC製程,是極為關鍵的製程技術。

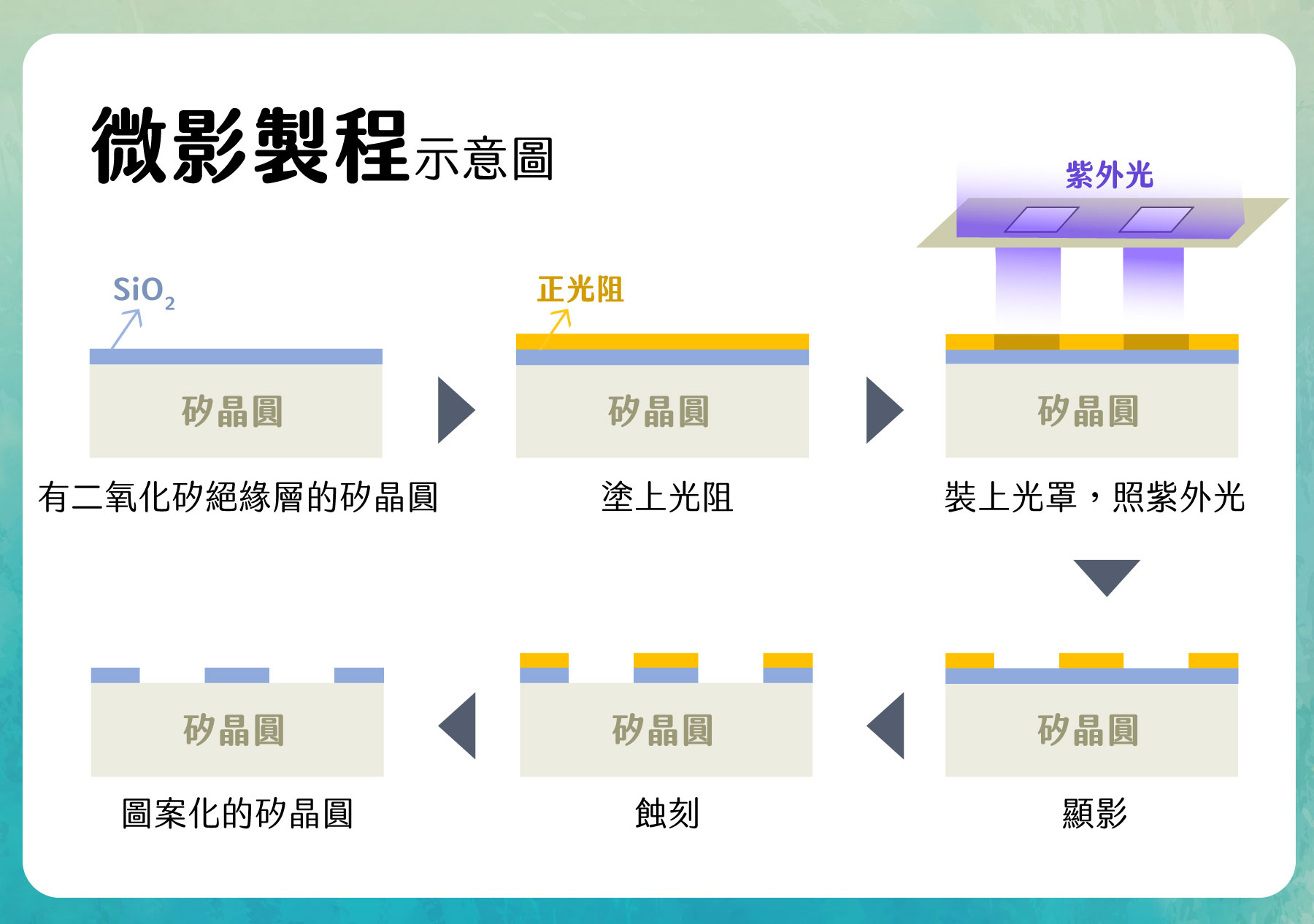

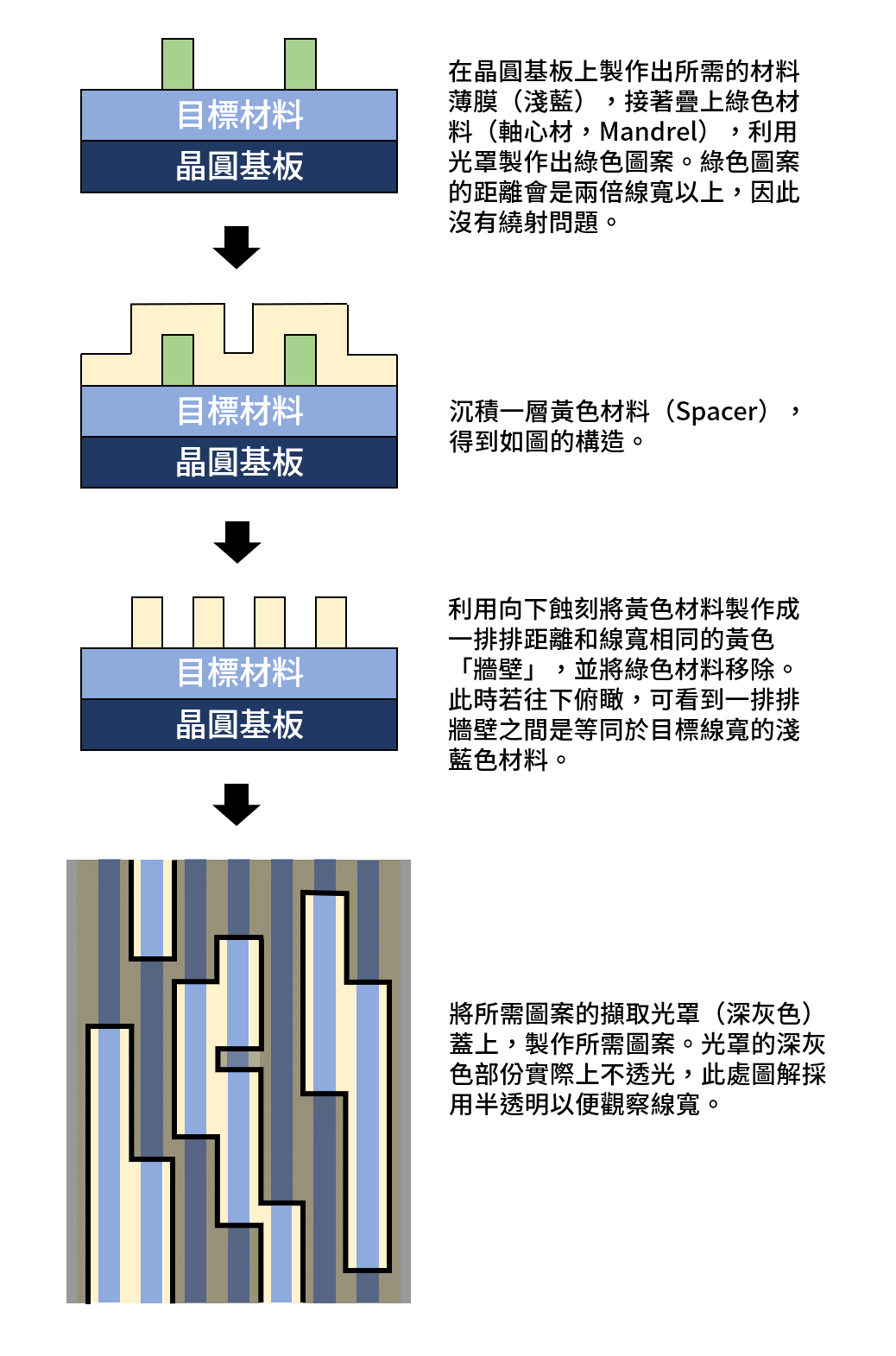

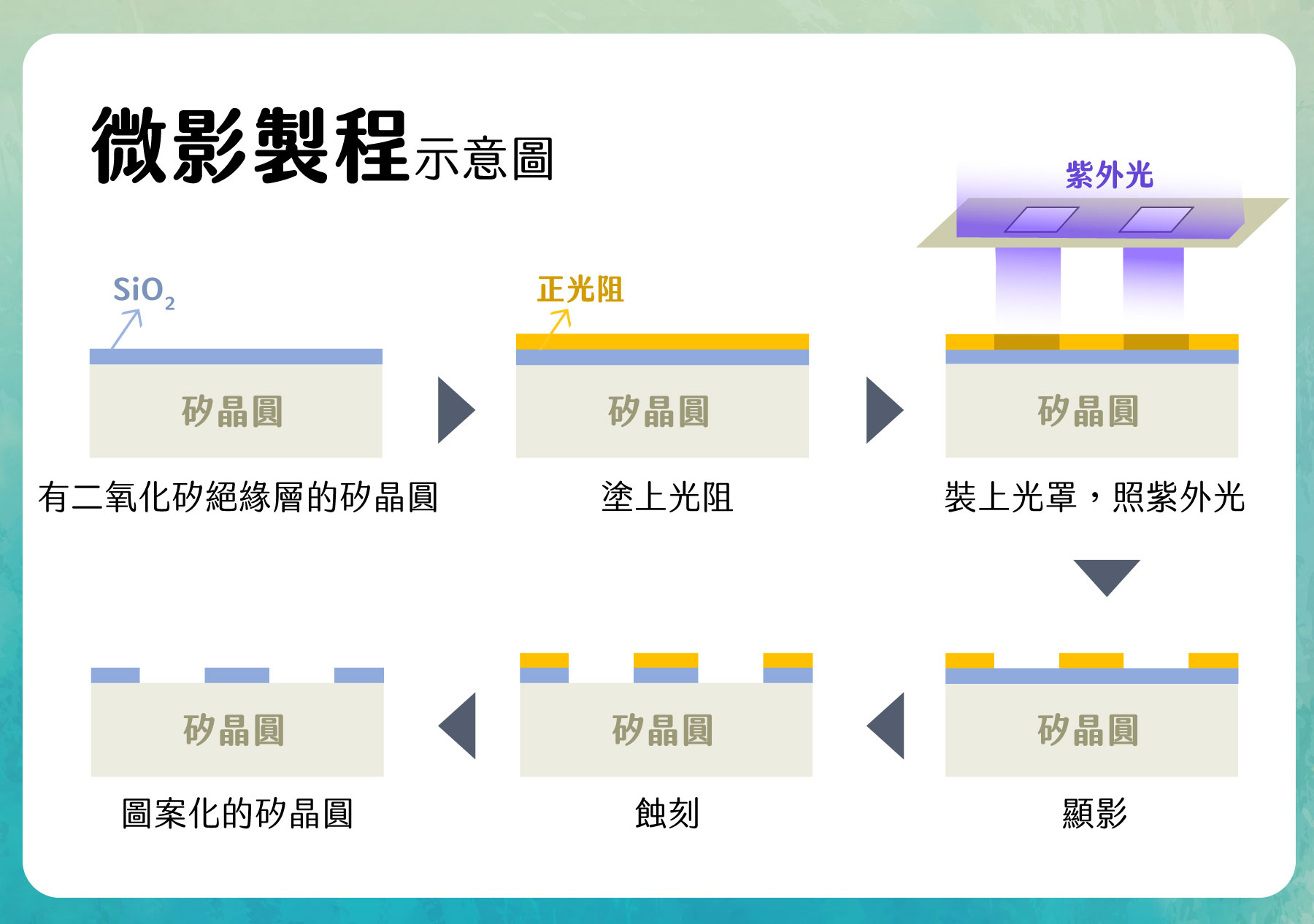

微影製程是將電路圖案,透過已刻好圖案的光罩及光阻,「轉印」到晶圓上的過程。舉例來說,在已有一層二氧化矽薄膜的晶圓上(見下圖),我們希望在特定位置蝕刻出一個洞,方法便是先在二氧化矽上塗布一層光阻,接著在上方放著光罩,光罩上大部分地方都是遮住的,只有在洞的位置可以讓光通過。照光之後,被光照過的光阻會變得容易溶解,接下來把該處的光阻以顯影液溶解掉,然後進行蝕刻,就可以只蝕刻到該特定位置的二氧化矽,其他地方的二氧化矽會被光阻保護著。等到蝕刻完畢,將剩餘的光阻清除,就完成了一次微影製程。

簡易的微影製程示意圖,主要就是將電路圖案「轉印」到晶圓上的過程。(圖/簡克志、孔瀞慧繪)

簡易的微影製程示意圖,主要就是將電路圖案「轉印」到晶圓上的過程。(圖/簡克志、孔瀞慧繪)

這是一個簡單的例子,在真實情況中,光罩上會有密密麻麻極為精細的電路圖案,不會只有一個洞;整個製程因為需要堆疊上各式各樣的材料,所以至少得做六次以上的微影,且每次使用的光罩都不一樣;此外,光阻也不一定是照光會變得比較容易溶解的「正光阻」,也可以是照光反而會變得堅硬的「負光阻」,端看製程需求而定。

一個光罩不夠,你可以用兩個—多圖案微影

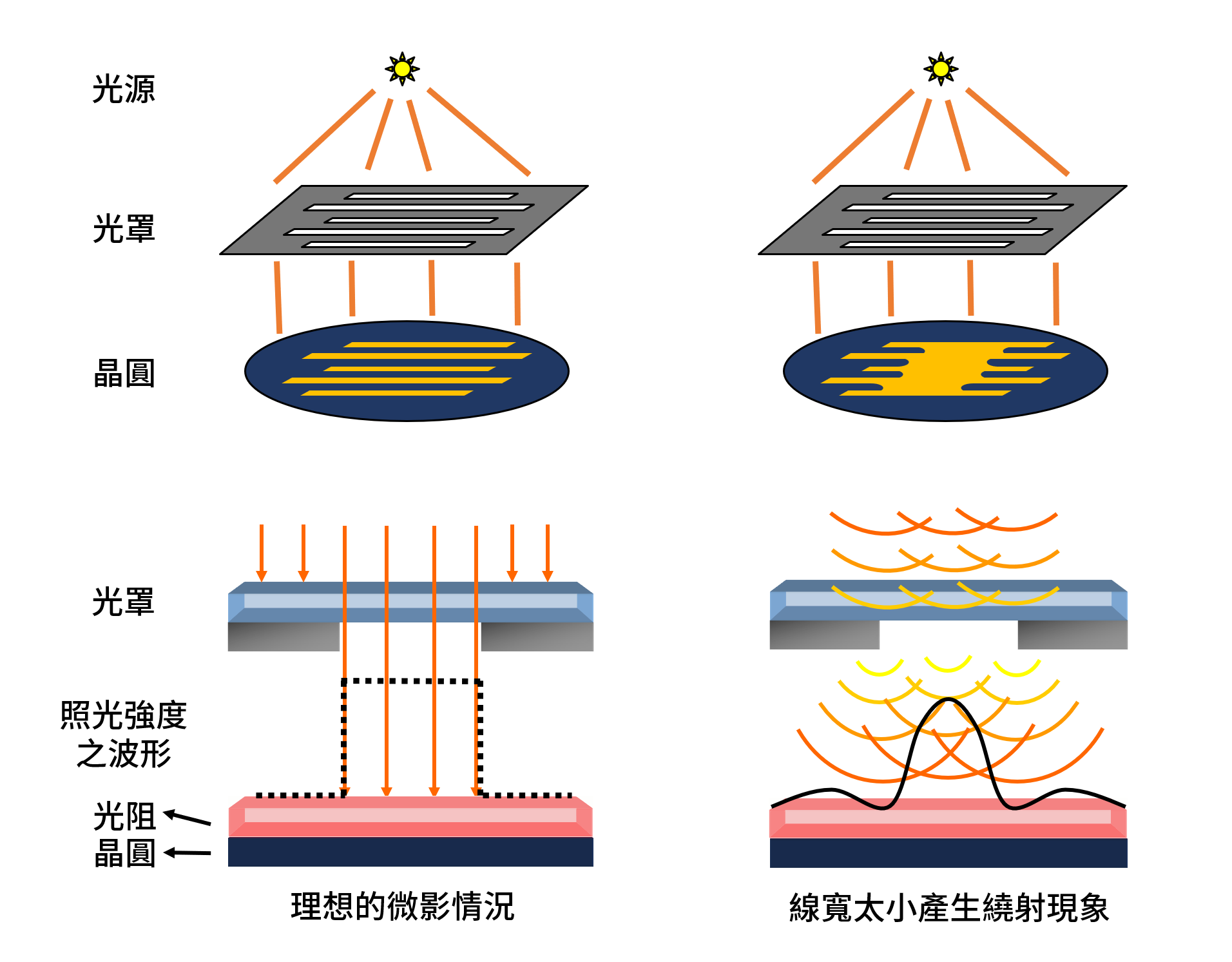

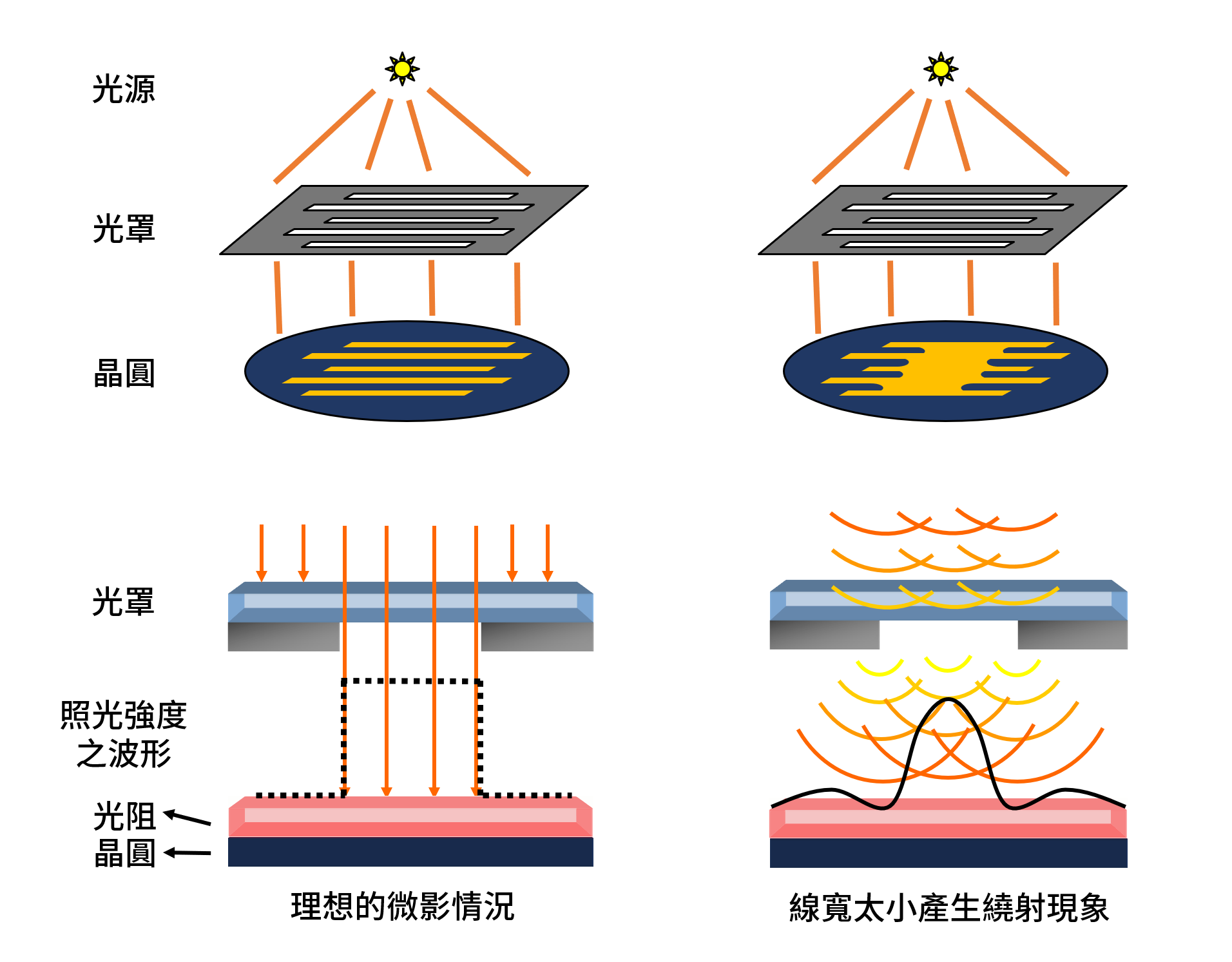

在元件愈做愈小的情況下,微影也必須配合元件尺寸,做出線寬很細、又很密集的電路圖案,但是因為一般微影製程使用的是波長193奈米的紫外光,在製造小於32奈米的線寬時,這個波長的光穿過光罩縫隙會產生繞射現象,使得照射範圍往外擴展一點點,但因為線的分布也很緊密,因此就容易使得線黏在一起,就像解析度不足的照片一樣,圖案變得模糊不清。

在小於32奈米的微影製程,光源穿過光罩縫隙會產生繞射現象,使得顯影區域互相覆蓋,圖案變得模糊不清。(圖/方劭云提供,簡克志改作)

在小於32奈米的微影製程,光源穿過光罩縫隙會產生繞射現象,使得顯影區域互相覆蓋,圖案變得模糊不清。(圖/方劭云提供,簡克志改作)

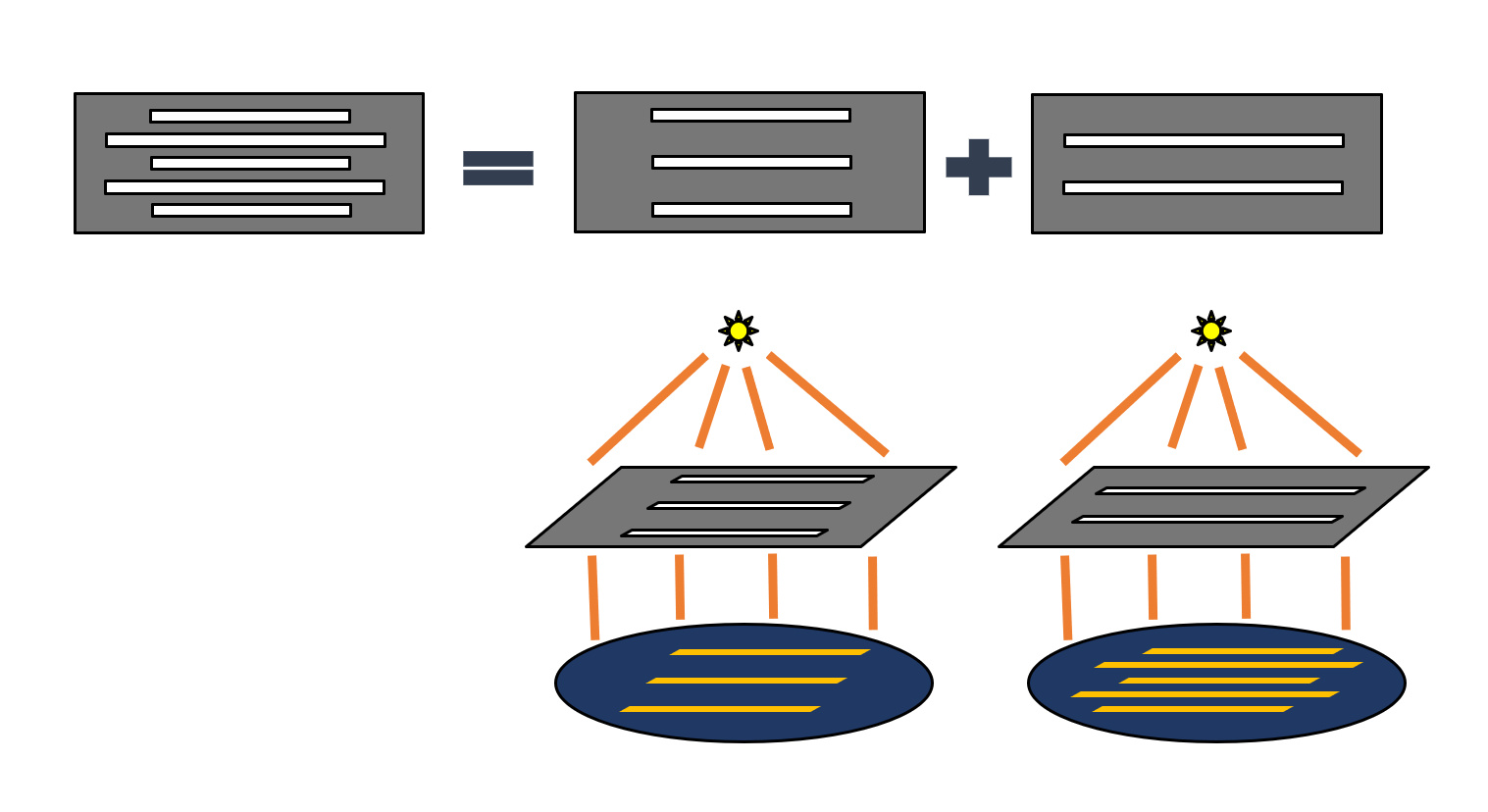

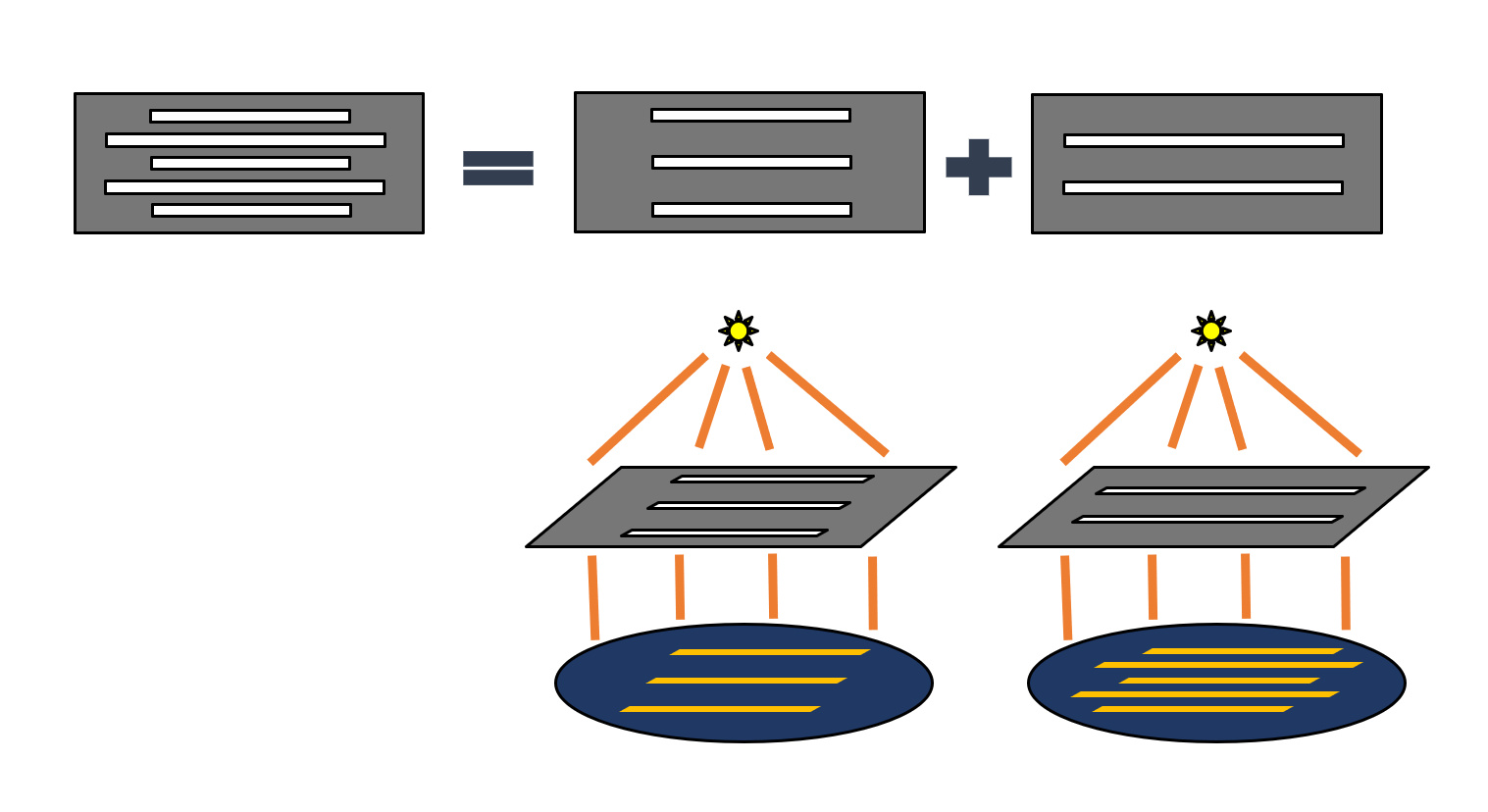

現在已經針對這類問題提出許多「解析度增進技術」(Resolution Enhancement Technology, RET),其中一項最主要的技術是「多圖案微影」,也就是將同一個圖案分成兩個以上的光罩,雖然這代表必須做兩次以上的微影曝光,但每個光罩上的洞和洞之間的距離會拉大,就可以避免線黏在一起。

多圖案微影,目的是為了避免因為線寬太細太密集導致的繞射現象,但是也有成本高和光罩對不準的問題。(圖/方劭云提供,簡克志改作)

多圖案微影,目的是為了避免因為線寬太細太密集導致的繞射現象,但是也有成本高和光罩對不準的問題。(圖/方劭云提供,簡克志改作)

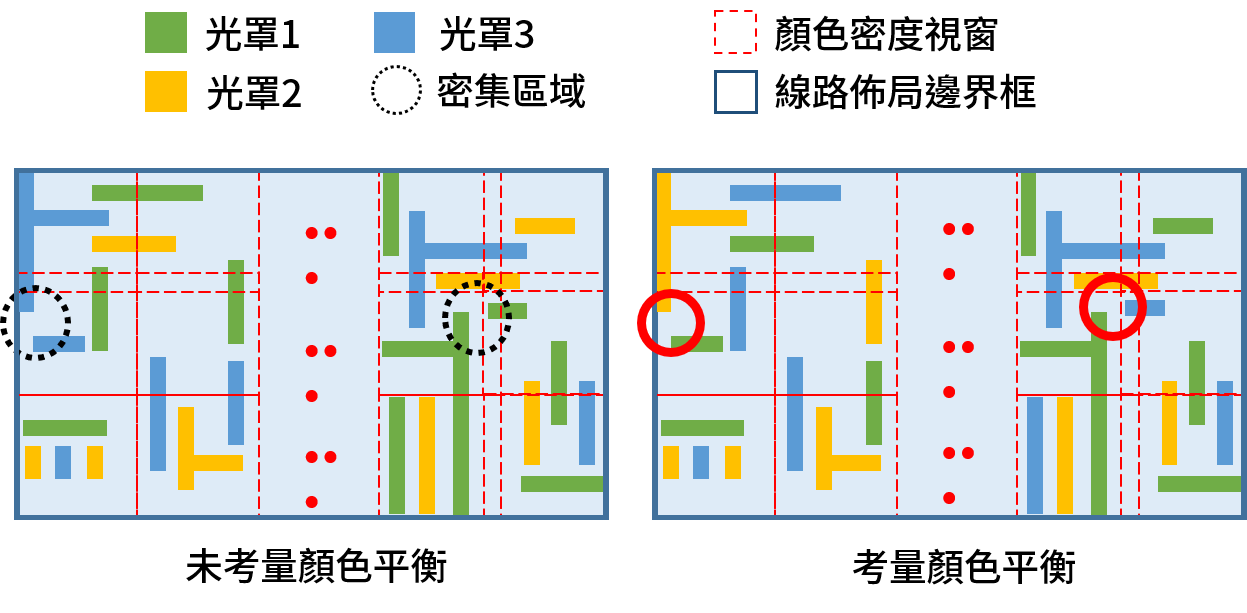

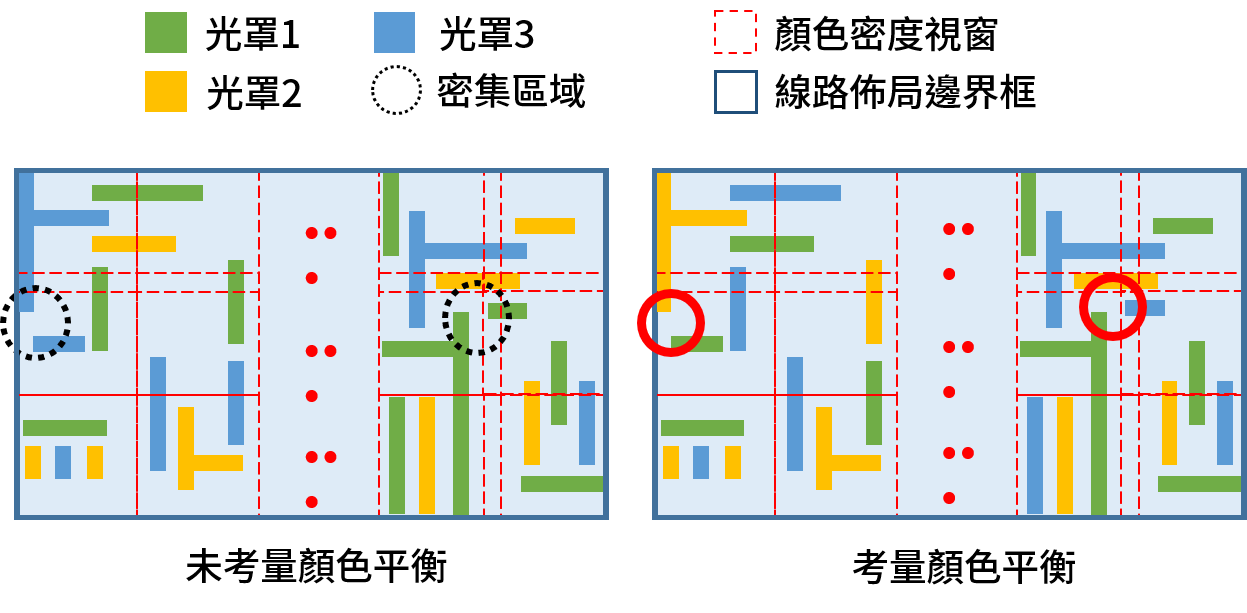

當光罩必須分成兩個以上時,這幾個光罩的圖案如何設計分配,是方劭云的研究主題之一。多圖案微影在設計光罩時會有許多條件,比如兩個洞的距離如果太小,就要分在不同光罩上,以不同顏色表示。另外,每個光罩在同一個局部區域的孔洞分布比例最好差不多,這樣曝光結果會比較完美,稱為「顏色的平衡度」。方劭云說:「我們從一開始的考量如何著色,後來慢慢開始考量顏色的平衡,現在又進一步考量怎麼在設計階段就注意顏色的平衡。」

不只考慮線路佈局,也需要將線路均勻分配給不同光罩,減少製程誤差。(圖/方劭云提供,簡克志中文化)

不只考慮線路佈局,也需要將線路均勻分配給不同光罩,減少製程誤差。(圖/方劭云提供,簡克志中文化)

多圖案微影有一個致命缺點—當光罩一多,就不容易對準。所以,雖然理論上既然有了多圖案微影,線寬再小都不怕,反正把光罩數量往上加就好;但實際上,不同的光罩不可能每一次放置的位置都完全一樣.一定會有一點對不準,光罩數量愈多,對不準的問題就愈嚴重,方劭云說:「多圖案微影做到四個光罩就已經很不準了。」

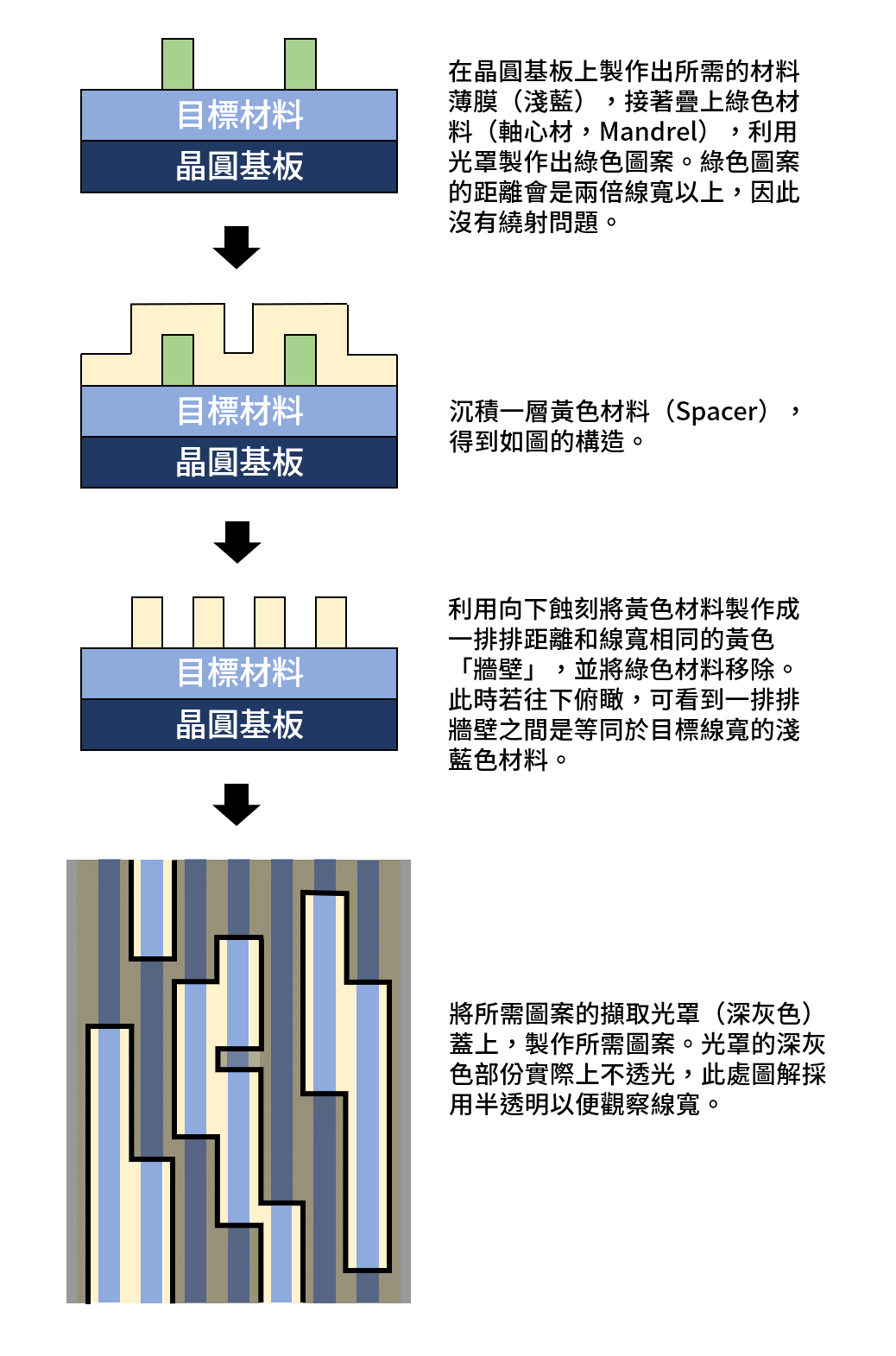

方劭云的另一項主要研究「自對準多圖案微影」(Self-Aligned Multiple

Patterning, SAMP),目的就是解決這個問題。這個做法巧妙地利用沉積與蝕刻技術,先製造出又細又密集的一排排「牆壁」,再用光罩將所需的圖案製作出來。這樣做的最大優點,在於細細的線並不是用光罩曝出來的,因此不會發生光罩對不準的問題。方劭云並且補充這個做法的另一個優點,就是後續以光罩製造所需圖案時,即使位置歪了一點點也沒有關係。

自對準多圖案微影圖解。(圖/方劭云提供,簡克志改作)

自對準多圖案微影圖解。(圖/方劭云提供,簡克志改作)

自動形成完美形狀—定向自組裝技術

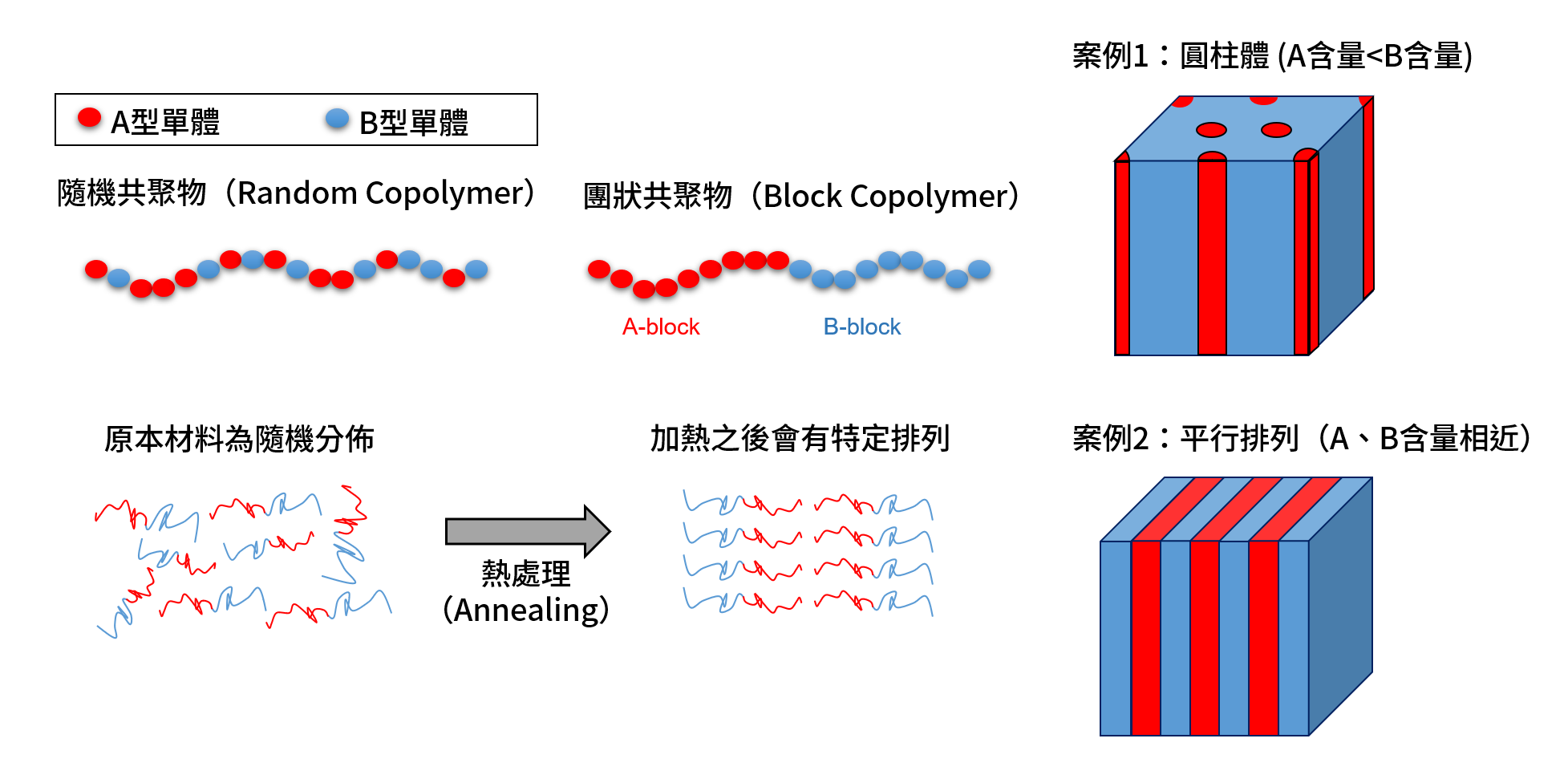

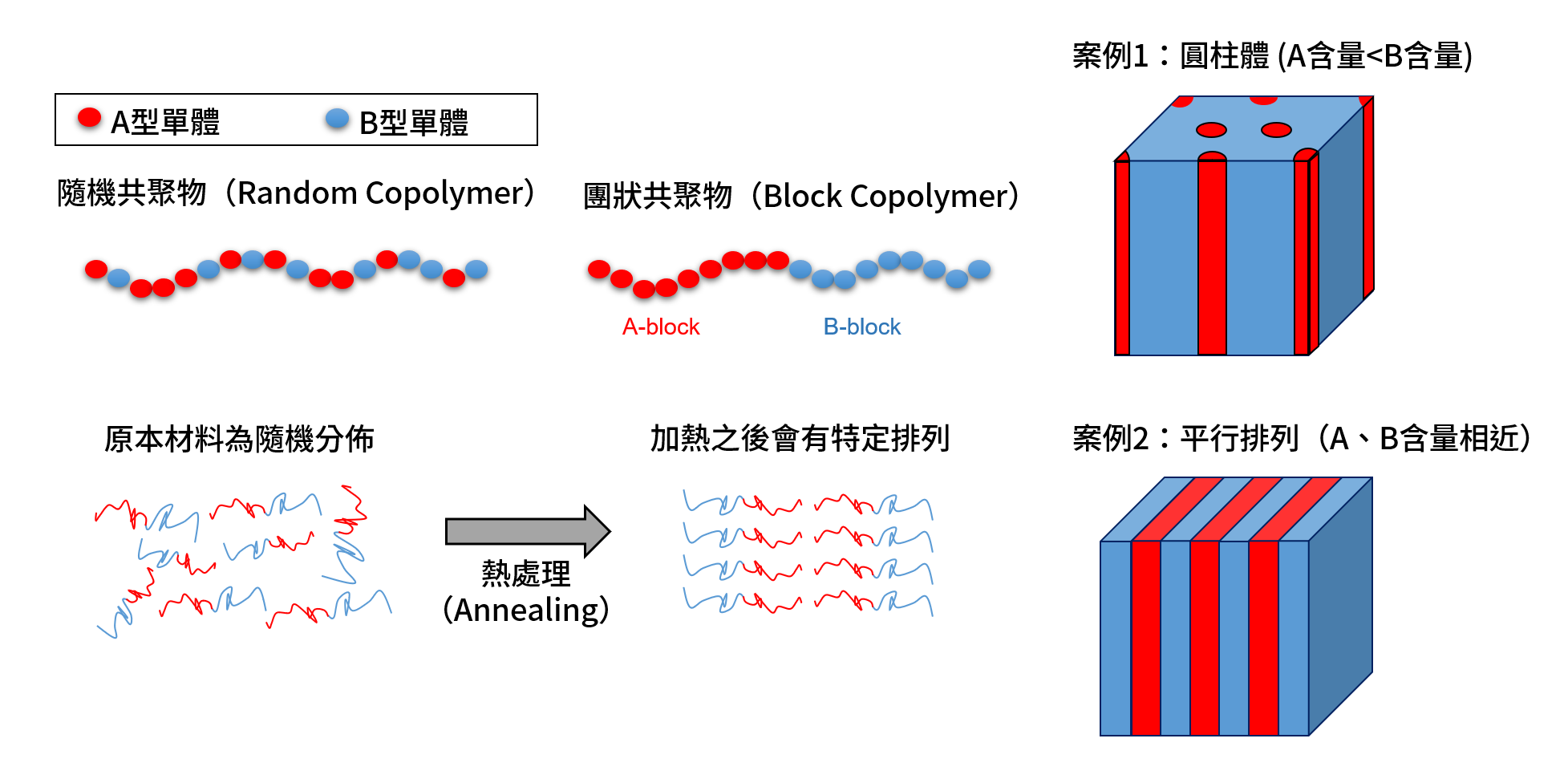

方劭云的另一個研究「定向自組裝技術」(Directed Self-Assembly, DSA),使用團狀共聚物(Block Copolymer)做為微影製程的材料,也對於增進解析度有很大的幫助。團狀共聚物會包含兩種材料A、B,一開始這兩種材料會在共聚物中隨機分布,然而在經過加熱後,兩種材料會各自聚在一起,形成特定的分布形狀。

舉例來說,在聚苯乙烯-聚甲基丙烯酸甲酯(PS-PMMA)這種材料中,當「聚苯乙烯」較「聚甲基丙烯酸甲酯」少時,加熱後的聚苯乙烯會自動聚成好幾條直徑只有幾奈米的圓柱體,分布在聚甲基丙烯酸甲酯之中,並且會根據整體的形狀,自動產生間隔;若兩種材料組成一樣多,加熱後則會交錯排列,像千層蛋糕一樣。方劭云解釋:「製造出來的圓柱體可以做成導通孔,一排一排的結構則可以做金屬線。」團狀共聚物材料這種特殊的性質,使得材料自己形成製程想要的細小尺寸,並且還自己隔開一個距離,完成微影製程中最困難的部分,製程人員只要在所需的地方打洞,填入這類材料,就可以得到比洞還要細小的結構。

定向自組裝使用團狀共聚物做為微影製程的材料,設定兩種材料A、B,一開始是隨機分佈,經過加熱處理之後,兩種材料會自動形成特定形狀。(圖/方劭云提供,簡克志改作)

定向自組裝使用團狀共聚物做為微影製程的材料,設定兩種材料A、B,一開始是隨機分佈,經過加熱處理之後,兩種材料會自動形成特定形狀。(圖/方劭云提供,簡克志改作)

DSA跳脫了傳統使用光罩的微影製程,不同的團狀共聚物得到的圓柱體大小、間隔也不盡相同。方劭云說:「這個做法著重的是材料的研發,也是微影製程未來很重要的發展角度。」

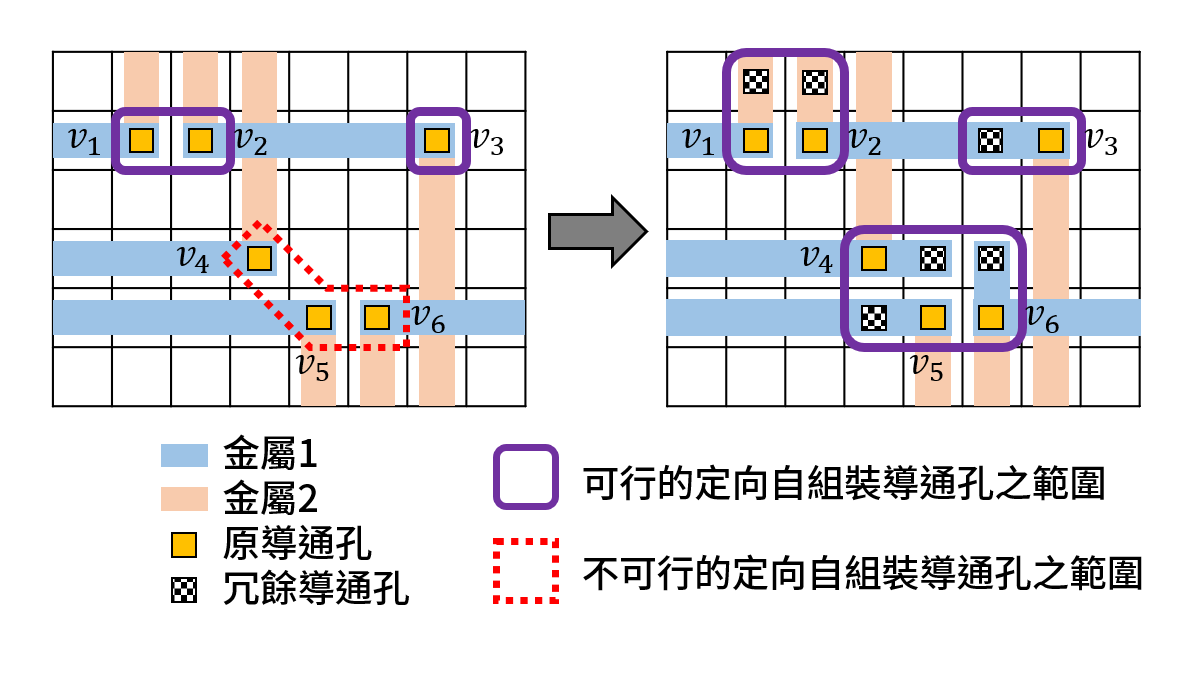

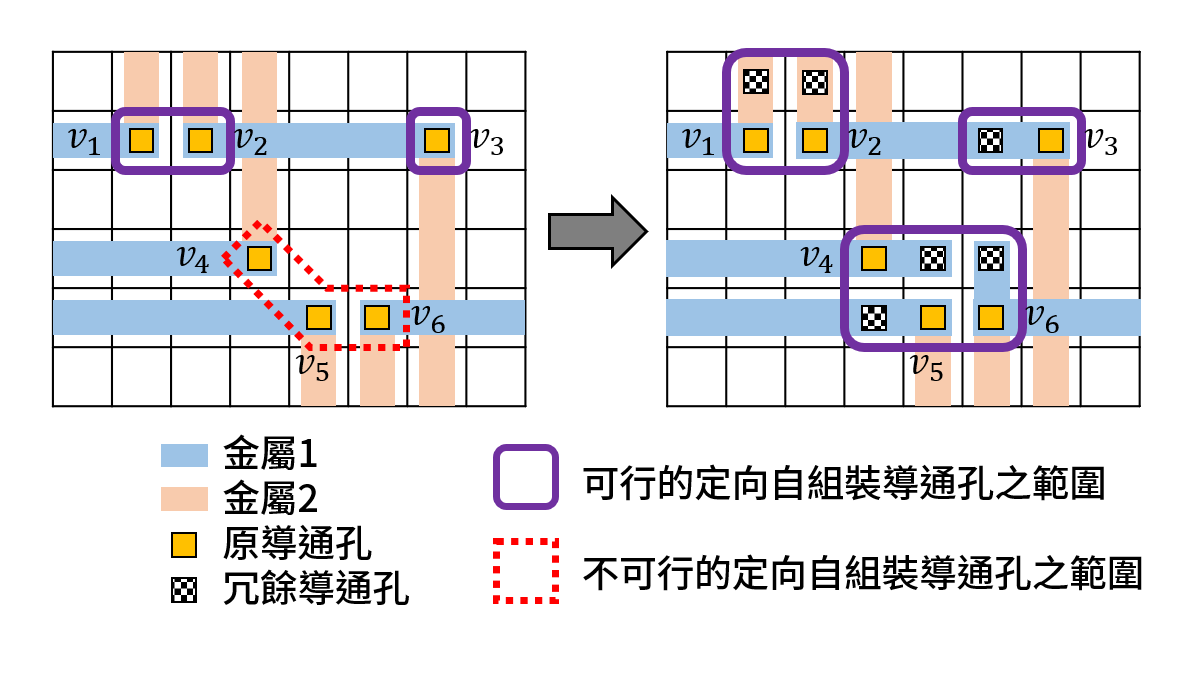

方劭云進一步說明,DSA對於電路設計會產生新的限制,因為圓柱體的分布有一定的規則,因此在選擇填洞位置及尺寸、形狀時,必須考慮圓柱體的分布特性。舉例來說,洞的形狀最好是方形或長方形,不能有不規則形狀.否則圓柱體產生的位置可能不夠準確。

使用定向自組裝技術時,需要考慮材料的特定排列方式,分佈不均勻的圖形設計在製程上會很容易失敗,上圖即為可行與不可行的導通孔範圍案例。(圖/方劭云提供,簡克志改作)

使用定向自組裝技術時,需要考慮材料的特定排列方式,分佈不均勻的圖形設計在製程上會很容易失敗,上圖即為可行與不可行的導通孔範圍案例。(圖/方劭云提供,簡克志改作)

製程太複雜,人工智慧來幫忙

在做IC設計時,必須符合所謂的「設計規範」,包括線和線之間的距離、線寬的最小尺寸、元件彼此不可短路等。方劭云說:「這類規範有上百條,都是設計時必須滿足的。」然而一個電路板上可能有高達上百萬個元件,要找出可能會違反設計規範的地方(Design Rule Violation, DRV)非常困難,因此這項工作需要人工智慧來幫忙。

方劭云舉例說,在做IC設計時,第一步是先擺放元件,第二步則是依據需求把元件之間連上金屬線。理想的狀況下,元件的擺放方式必須讓之後連線時不會出現DRV,「但這非常困難,因為擺元件與連金屬線是兩個分開的步驟,在擺的時候根本不知道線會怎麼繞。」所以,我們需要用機器學習的方式,訓練出一個能夠預測DRV會在哪裡出現的模型。

在訓練模型時可以先納入某些直觀的特徵,例如元件接腳密度愈高,出錯機率就愈大。另一個做法就是先把整個電路先切分成許多較大的範圍,粗略的連線看看是否會出錯。此外,方劭云的團隊也發現某些元件擺放的方式特別容易發生DRV,因此也納入訓練模型中。

人工智慧與機器學習在製程上的應用,還包括了改進光罩設計,補償在光罩孔洞邊邊角角會發生光量不足的問題(稱為光學鄰近效應);另外也可以協助導通孔的設計,應用非常廣泛。

國立臺灣科技大學電機系副教授方劭云獲得科技部109年度吳大猷獎。(圖/簡克志攝)

國立臺灣科技大學電機系副教授方劭云獲得科技部109年度吳大猷獎。(圖/簡克志攝)

一種微影技術不夠,你也可以用兩種!

儘管有上述這些技術研究,然而近期微影製程正在迎接的,是另一項極重要的進展—13.5奈米的極紫外光光源(Extreme Ultraviolet, EUV)。這種波長極小的光,直接暴力解決了繞射問題,不需要使用多圖案微影技術,就能製造出最小達7奈米的線寬。

不過,為了遵循摩爾定律(

註1),半導體製程未來還得將元件不斷縮小下去,根據「國際設備和系統藍圖」(International Roadmap for Devices and Systems, IRDS)這個組織的製程建議,在金屬線寬8奈米以下可以使用EUV搭配雙圖案微影,在更小的尺寸則建議使用EUV搭配DSA。換句話說,這些微影技術可以相互配合,來達成縮小元件的目標。

那麼,這些微影技術真的可以讓我們一直跟著摩爾定律走下去嗎?方劭云說:「如果我們的目標是『遵從摩爾定律』,那還有一些技巧可以使用,例如把電晶體堆疊起來,或是改變電晶體的結構。」另一方面,線寬最終還是會遇到極限,可能在1奈米左右,「或許我們到時候真的得使用量子電腦。」方劭云說,未來的變化現在難以預測,不過這也讓研究人員永遠不愁有新的題目可以鑽研!

註1:摩爾定律來自英特爾創始人之一摩爾(Gordon Moore)於1965年所發表的一份觀察報告,內容指出積體電路單位面積上可容納的電晶體數目,約每隔兩年便會增加一倍。

簡易的微影製程示意圖,主要就是將電路圖案「轉印」到晶圓上的過程。(圖/簡克志、孔瀞慧繪)

簡易的微影製程示意圖,主要就是將電路圖案「轉印」到晶圓上的過程。(圖/簡克志、孔瀞慧繪) 在小於32奈米的微影製程,光源穿過光罩縫隙會產生繞射現象,使得顯影區域互相覆蓋,圖案變得模糊不清。(圖/方劭云提供,簡克志改作)

在小於32奈米的微影製程,光源穿過光罩縫隙會產生繞射現象,使得顯影區域互相覆蓋,圖案變得模糊不清。(圖/方劭云提供,簡克志改作) 多圖案微影,目的是為了避免因為線寬太細太密集導致的繞射現象,但是也有成本高和光罩對不準的問題。(圖/方劭云提供,簡克志改作)

多圖案微影,目的是為了避免因為線寬太細太密集導致的繞射現象,但是也有成本高和光罩對不準的問題。(圖/方劭云提供,簡克志改作) 不只考慮線路佈局,也需要將線路均勻分配給不同光罩,減少製程誤差。(圖/方劭云提供,簡克志中文化)

不只考慮線路佈局,也需要將線路均勻分配給不同光罩,減少製程誤差。(圖/方劭云提供,簡克志中文化) 自對準多圖案微影圖解。(圖/方劭云提供,簡克志改作)

自對準多圖案微影圖解。(圖/方劭云提供,簡克志改作) 定向自組裝使用團狀共聚物做為微影製程的材料,設定兩種材料A、B,一開始是隨機分佈,經過加熱處理之後,兩種材料會自動形成特定形狀。(圖/方劭云提供,簡克志改作)

定向自組裝使用團狀共聚物做為微影製程的材料,設定兩種材料A、B,一開始是隨機分佈,經過加熱處理之後,兩種材料會自動形成特定形狀。(圖/方劭云提供,簡克志改作) 使用定向自組裝技術時,需要考慮材料的特定排列方式,分佈不均勻的圖形設計在製程上會很容易失敗,上圖即為可行與不可行的導通孔範圍案例。(圖/方劭云提供,簡克志改作)

使用定向自組裝技術時,需要考慮材料的特定排列方式,分佈不均勻的圖形設計在製程上會很容易失敗,上圖即為可行與不可行的導通孔範圍案例。(圖/方劭云提供,簡克志改作) 國立臺灣科技大學電機系副教授方劭云獲得科技部109年度吳大猷獎。(圖/簡克志攝)

國立臺灣科技大學電機系副教授方劭云獲得科技部109年度吳大猷獎。(圖/簡克志攝)