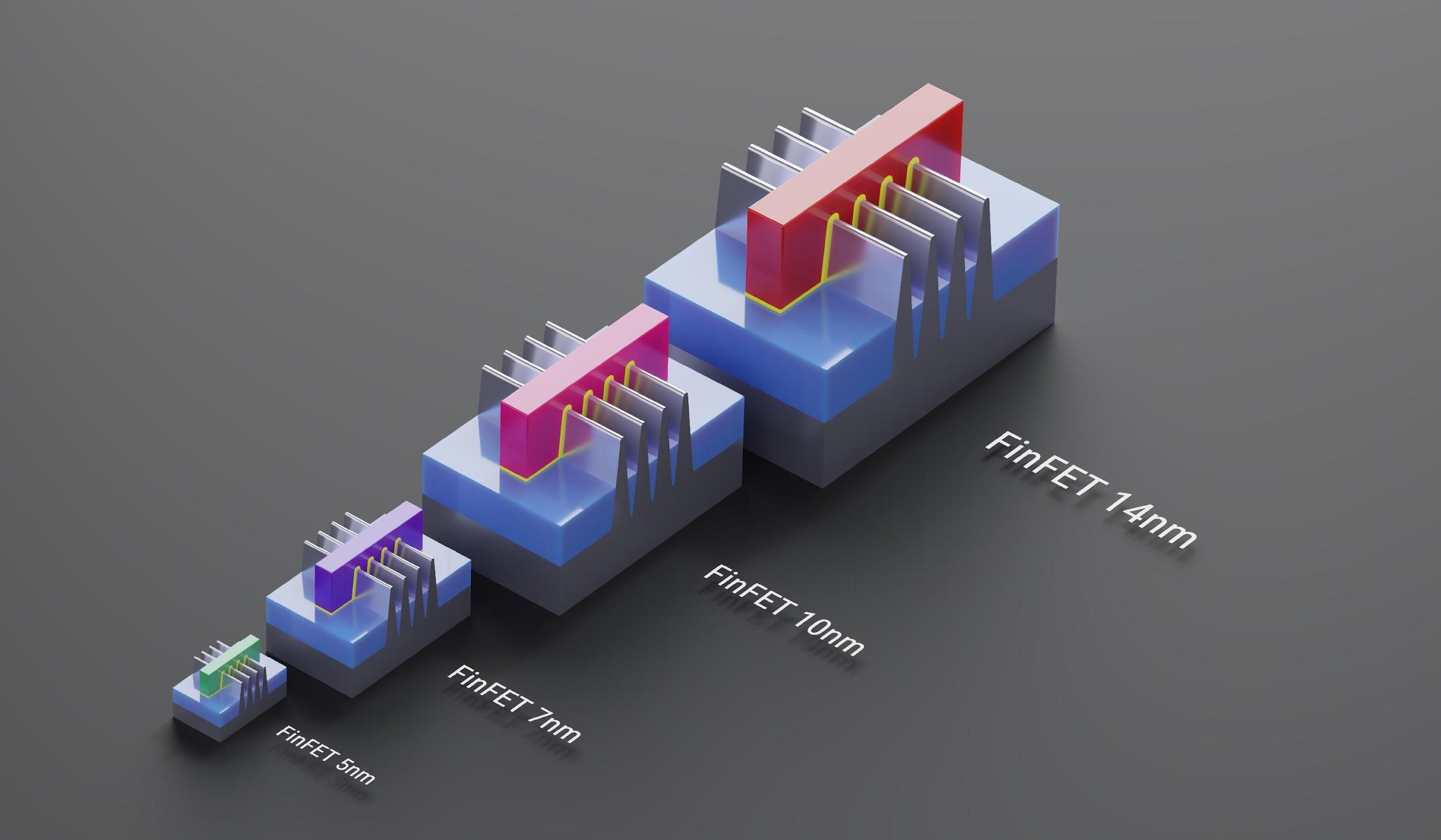

圖一:半導體先進製程競賽白熱化!全世界誰能在下一世代的技術節點取得領先?(影像來源:Shutterstock)

臺灣的半導體產業在全球占有極其關鍵的地位,面對先進製程競賽的白熱化,全世界的頂尖團隊皆積極投入研發,希望能在下一世代的技術節點取得領先。

隨著半導體元件製程技術的演進,元件架構從傳統的平面電晶體(Planar FET)發展至目前主流的鰭式電晶體(FinFET)。鰭式電晶體具有「三維」的立體結構,可提升元件的電流密度,並增強通道的控制能力,降低元件功耗。

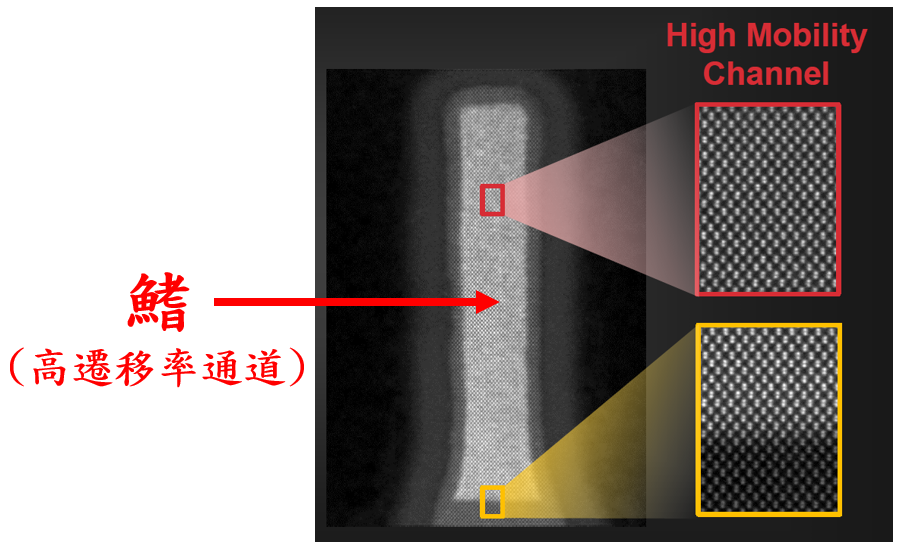

「高遷移率通道」如駕駛跑車!電晶體速度更快、效能更強

圖二為台積電於2021年國際固態電路研討會(ISSCC)中所展示之5奈米技術節點的高遷移率通道(high mobility channel)鰭式電晶體[1],使用高遷移率通道,猶如駕駛跑車,速度更快,使電晶體的效能更強。台積電目前已量產的5奈米技術節點,以及今年即將問世的3奈米技術節點皆採用鰭式電晶體的結構。

圖二:台積電5奈米技術節點的高遷移率通道鰭式電晶體[1]。(影像來源:IEEE)

「閘極環繞式」結構如同滴水不漏水龍頭!讓電晶體更加節能省電

當電晶體的尺寸繼續變小,因製程微縮造成漏電流等問題產生,必須改變電晶體的架構以增強通道的控制能力。

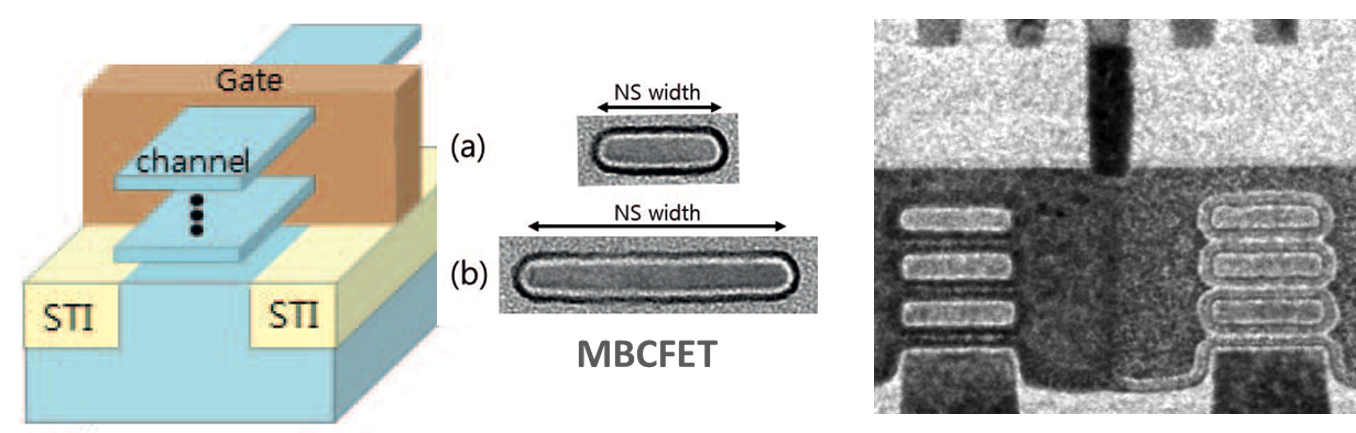

三星(Samsung)率先宣布在3奈米技術節點採用閘極環繞式(Gate-All-Around, GAA)的多橋通道電晶體(Multi-Bridge-Channel FET, MBCFET)結構(圖三左、中)[2],MBCFET的結構與多層橋梁相似,和閘極環繞的堆疊奈米片(Stacked Nanosheets)是相同的結構。

台積電在2021 ISSCC國際會議上展示三層垂直堆疊奈米片作為2奈米技術節點的電晶體結構(圖三右)[1]。閘極環繞式電晶體具有比鰭式電晶體更好的通道控制能力,使用閘極環繞式電晶體結構,猶如滴水不漏的水龍頭,可使電晶體有效降低漏電流,更加節能省電。

(右)台積電2奈米技術節點之三層垂直堆疊奈米片電晶體[1]。(影像來源:IEEE)

臺灣研究團隊取得重大突破,大幅超越業界現有堆疊技術

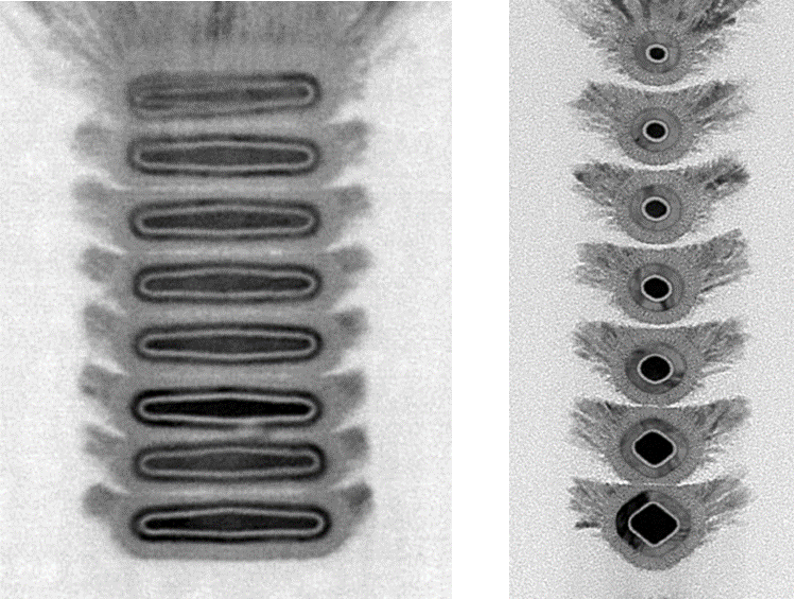

為了增加電晶體的驅動電流,提升元件效能,採用通道堆疊(channel stacking)的方法,在垂直方向增加通道數目,如同多層高架橋,在相同占地面積下,可承載更多車流量,使電晶體驅動電流更大。台積電2奈米技術節點使用三層垂直堆疊奈米片電晶體(圖三右),本研究團隊則突破現有的堆疊技術,研究高遷移率高層數的三維電晶體,預計2025年達24層,大幅超越業界現有的堆疊技術,持續推進技術節點之微縮。

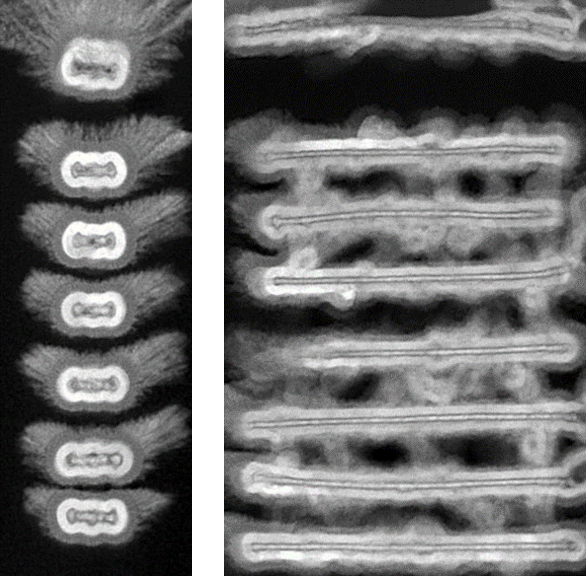

本研究團隊優化磊晶(epitaxy)與蝕刻(etching)製程,成功整合「高遷移率通道」、「高層數垂直堆疊」與「三維閘極環繞式電晶體」,並於2021年超大型積體電路技術研討會(VLSI)中發表了八層堆疊鍺矽N型奈米片電晶體(8 stacked Ge0.75Si0.25 nanosheets) (圖四左)[3]和世界首顆高效能七層鍺矽N型奈米線電晶體(7 stacked Ge0.95Si0.05 nanowires) (圖四右)[3],此研究成果也榮獲國際頂尖期刊自然電子學(Nature Electronics)研究亮點(Research Highlight)報導[4]。

圖四:本研究團隊發表之(左)八層堆疊鍺矽奈米片與(右)七層鍺矽奈米線電晶體[3]。(影像來源:IEEE)

製備出 3 奈米極薄通道降低元件漏電流,創下世界紀錄

P型電晶體(編按:p-type semiconductor,又稱「電洞型半導體」)方面,本研究團隊在2021年國際電子元件會議(IEDM)上發表七層與八層堆疊鍺錫極薄通道電晶體(7 stacked and 8 stacked Ge0.9Sn0.1 ultrathin bodies) (圖五)[5],製備出厚度為3奈米之極薄通道,有效降低元件之漏電流,其開關電流比為鍺/鍺錫三維電晶體之世界紀錄,此篇論文也獲得2021 IEDM最佳學生論文獎(Roger A. Haken Best Student Paper Award)。

圖五:本研究團隊發表之(左)七層與(右)八層鍺錫極薄通道電晶體[5]。(影像來源:IEEE)

二維材料電晶體目前仍有努力空間

鍺(Ge)、鍺矽(GeSi)、鍺錫(GeSn)等矽基材料,具有優於矽(Si)的載子遷移率,可增加電晶體的驅動電流,並且與現今業界的矽半導體製程技術有良好的相容性,具有成為下世代通道材料的潛力。

其他非矽基的新穎材料,如二維材料(2D Material),因為單層原子的特性,許多人對其微縮的潛力寄予厚望,在自然期刊(Nature)[6]以及IEDM國際會議[7]上皆有相關的論文探討。

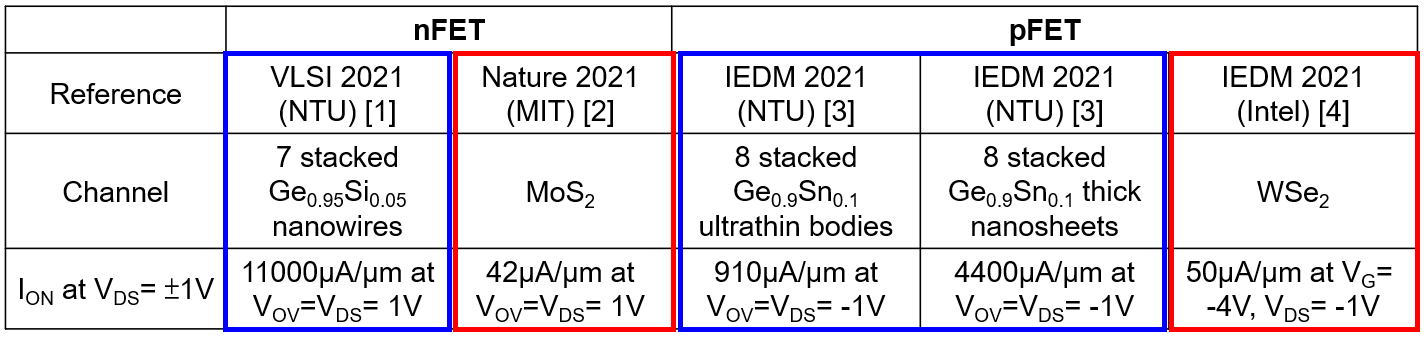

然而,二維材料面臨了大面積高品質的晶圓成長技術挑戰,以及高接觸電阻(約1E-8Ω-cm2, 矽基約1E-9Ω-cm2)、低電流(表一)等諸多問題。二維材料在元件製程上難以與業界成熟之矽基材料或奈米片三維電晶體結構相容,在元件效能的表現上也較矽基電晶體有差距。雖然已有新聞發表,號稱可用於1奈米技術節點,但仍然需要努力。

表一:矽基材料(藍框處)與二維材料(紅框處)之比較。二維材料電晶體的驅動電流(ION)遠小於矽基電晶體。(影像來源:劉致為教授提供)

● [1] Mark Liu, “Unleashing the Future of Innovation,” 2021 IEEE International Solid-State Circuits Conference (ISSCC), Plenary Session 1.1, 2021.

● [2] G. Bae et al., “3nm GAA Technology featuring Multi-Bridge-Channel FET for Low Power and High Performance Applications,” IEEE International Electron Devices Meeting (IEDM), pp. 656-659, 2018.

● [3] Y.-C. Liu et al., “First Highly Stacked Ge0.95Si0.05 nGAAFETs with Record ION = 110 μA (4100 μA/μm) at VOV=VDS=0.5V and High Gm,max = 340 μS (13000 μS/μm) at VDS=0.5V by Wet Etching,” IEEE Symposia on VLSI Technology and Circuits (VLSI), T15-2, 2021.

● [4] S. Thomas, “Germanium nanowire transistors stack up,” Nature Electronics, Vol. 4, July 2021, 452.

● [5] C.-E. Tsai et al., “Highly Stacked 8 Ge0.9Sn0.1 Nanosheet pFETs with Ultrathin Bodies (~3nm) and Thick Bodies (~30nm) Featuring the Respective Record ION/IOFF of 1.4x107 and Record ION of 92μA at VOV=VDS= -0.5V by CVD Epitaxy and Dry Etching,” IEEE International Electron Devices Meeting (IEDM), pp. 569-572, 2021.

● [6] P.-C. Shen et al., “Ultralow contact resistance between semimetal and monolayer semiconductors,” Nature, 593, 211-217, 2021.

● [7] K. P. O’Brien et al., “Advancing 2D Monolayer CMOS Through Contact, Channel and Interface Engineering,” IEEE International Electron Devices Meeting (IEDM), pp. 146-149, 2021.

本著作係採用 創用 CC 姓名標示─非商業性─禁止改作 3.0 台灣 授權條款 授權.

本授權條款允許使用者重製、散布、傳輸著作,但不得為商業目的之使用,亦不得修改該著作。 使用時必須按照著作人指定的方式表彰其姓名。

閱讀授權標章或

授權條款法律文字。