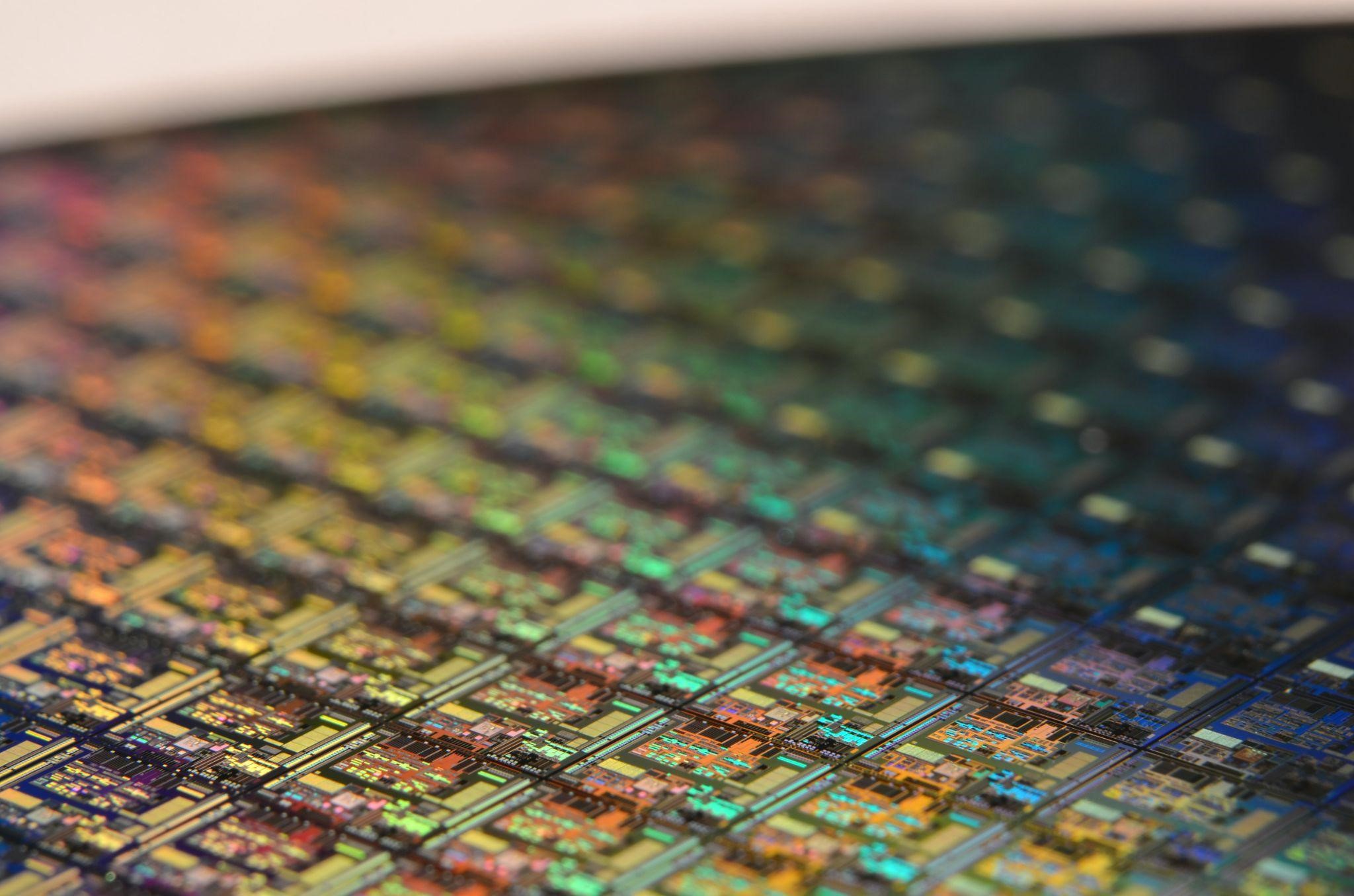

圖一:傳統上所稱的奈米製程技術節點,指的是電晶體元件的閘極通道長度,也常稱為閘極線寬。(影像來源:Shutterestock)

為提升半導體晶片速度、增加元件積集密度(Intergrated circuit density)並降低功耗,半導體元件持續不斷的微縮,進而引發許多問題,諸如短通道效應(short-channel effect)、穿隧效應(Tunneling Effect)、熱效應(Thermal effect)以及量子侷限效應(quantum confinement effect)等,因此摩爾定律(Moore’s Law)是否能持續向前推進一直是近幾年的熱門的議題。反觀半導體產業的製程技術,卻仍在各種質疑聲中不斷地向前推進,目前台積電已宣布 3 奈米製程將在 2022 下半年量產,而 2 奈米製程也預計在 2025 年量產。

元件尺度微縮是否有物理極限?

傳統上所稱的奈米製程技術節點,指的是電晶體元件的閘極(gate)通道長度,也常稱為閘極線寬。但實際上技術節點的數值與閘極線寬並不相等,尤其是在 20 奈米節點以下,閘極線寬其實是大於技術節點的數值。以目前 3 奈米技術節點而言,實際上閘極線寬仍維持在 10 奈米以上,主要是因為電晶體結構開始由平面式轉變成三維立體結構(如鰭式電晶體 FinFET 或閘極全環式電晶體 GAAFET),提升了通道電流控制能力,進而能達到 3 奈米以下的有效線寬。

在這種三維元件結構中,隨著節點技術的微縮,元件通道層厚度也必須隨之降低才能維持通道電流的控制能力。根據國際元件與系統技術藍圖,當到達 3 奈米以下技術節點,元件通道實際厚度也將達到 6 奈米以下。以目前矽基半導體元件而言,當通道層厚度小於 3 奈米時,電子在半導體通道中將因為表面粗糙的散射而無法有效的移動,也因此將面臨材料的物理極限。

面臨材料極限的替代方案

目前產業界仍不斷地開發新的元件結構(如高層數堆疊的奈米片或奈米線結構),試圖讓技術節點持續向下延伸。然而,尋找新的通道材料作為替代方案也是重要的選項。二維半導體材料,如二硫化鉬(MoS2)與二硫化鎢(WS2)等,僅有原子層的厚度(約 0.7 奈米)且其表面非常平整,使電子在材料中仍然可以高速遷移,也讓二維半導體材料成為 3 奈米以下技術節點重要的非矽通到材料。

但是以目前的技術而言,二維半導體材料及元件與目前的晶片技術整合仍有相當大落差,同時在材料合成生長與元件製作方面都存在許多技術瓶頸。在材料之合成生長技術方面,目前已經可以透過如化學氣相沉積(chemical vapor deposition,簡稱 CVD)等技術合成二維材料,但是其缺陷密度仍高(一般估計都高達 1012-1014 cm-2),因而大幅限制了材料的載子遷移率(carrier mobility)。此外,對於能達到產業應用等級的大面積單晶生長技術目前仍尚未成熟。

新材料、新契機、新挑戰

具備大面積高品質單晶生長技術,是實現二維材料於半導體工業應用的首要條件。雖然目前的生長技術已經可以合成晶圓尺寸的二維半導體薄膜,甚至達到大面積單晶的二維半導體生長。然而,對於薄膜缺陷密度的控制,仍然是極大挑戰。這些晶體中的缺陷會形成帶電的散射中心而影響電子傳輸特性,進而對電晶體元件特性產生不良影響。因此,如何降低缺陷密度仍然是發展電子元件的關鍵技術。

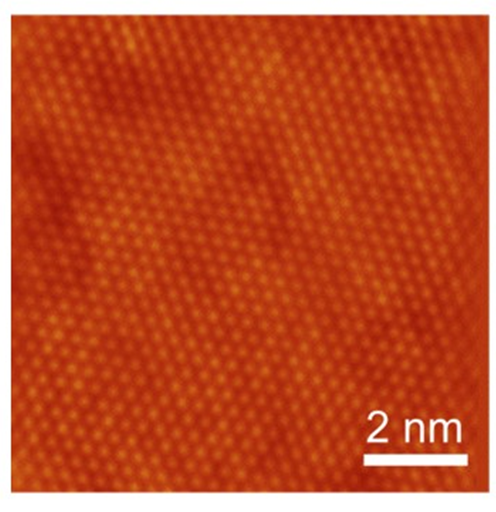

近年來,我們的研究團隊在單層二維氮化硼(boron nitride, BN)絕緣體層的合成有重要的進展,已經可以在 2 吋晶圓上先藉由形成單晶銅的表面,進而生長出 2 吋晶圓尺寸的單晶單層氮化硼。我們也透過類似的生長方法,在單晶的金表面生長單層二硒化鉬(MoSe2)二維半導體,以原子解析影像分析估計缺陷密度僅約 1.6x1010/cm2,比目前所報導以化學方法合成的缺陷密度至少低了 100 倍,顯示單晶金表面具有生長高品質二維半導體的潛力。

雖然二維半導體未來是否能與目前的晶片技術整合仍不得而知,目前國際間無論在學術界或半導體產業界,都已相繼投入二維半導體料與元件技術開發,而國內無論產官學界也都已經提早布局。二維半導體材料能否打破現有半導體元件框架,成為下世代前瞻半導體技術開展的新契機,仍然值得期待。

圖二:在單晶金表面生長單層二硒化鉬二維半導體之原子解析影像,具有極低點之缺陷密度(1.6×1010 cm-2)。

本著作係採用 創用 CC 姓名標示─非商業性─禁止改作 3.0 台灣 授權條款 授權.

本授權條款允許使用者重製、散布、傳輸著作,但不得為商業目的之使用,亦不得修改該著作。 使用時必須按照著作人指定的方式表彰其姓名。

閱讀授權標章或

授權條款法律文字。